MC68020RC16E Freescale Semiconductor, MC68020RC16E Datasheet - Page 194

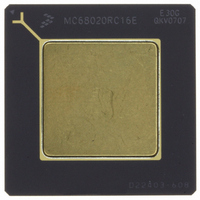

MC68020RC16E

Manufacturer Part Number

MC68020RC16E

Description

IC MPU 32BIT 16MHZ 114-PGA

Manufacturer

Freescale Semiconductor

Datasheet

1.MC68020EH16E.pdf

(306 pages)

Specifications of MC68020RC16E

Processor Type

M680x0 32-Bit

Speed

16MHz

Voltage

5V

Mounting Type

Surface Mount

Package / Case

114-PGA

Family Name

M68000

Device Core

ColdFire

Device Core Size

32b

Frequency (max)

16.67MHz

Instruction Set Architecture

RISC

Supply Voltage 1 (typ)

5V

Operating Supply Voltage (max)

5.25V

Operating Supply Voltage (min)

4.75V

Operating Temp Range

0C to 70C

Operating Temperature Classification

Commercial

Mounting

Through Hole

Pin Count

114

Package Type

CPGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Lead Free Status / Rohs Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC68020RC16E

Manufacturer:

MOT

Quantity:

900

Company:

Part Number:

MC68020RC16E

Manufacturer:

MOT

Quantity:

900

Part Number:

MC68020RC16E

Manufacturer:

MOTOROLA/摩托罗拉

Quantity:

20 000

- Current page: 194 of 306

- Download datasheet (3Mb)

7.4.12 Transfer to/from Top of Stack Primitive

The transfer to/from top of stack primitive transfers an operand between the coprocessor

and the top of the active system stack of the main processor. This primitive applies to

general and conditional category instructions. Figure 7-32 shows the format of the transfer

to/from top of stack primitive.

The transfer to/from top of stack primitive uses the CA, PC, and DR bits as described in

7.4.2 Coprocessor Response Primitive General Format. If the coprocessor issues this

primitive with CA = 0 during a conditional category instruction, the main processor initiates

protocol violation exception processing.

The length field of the primitive format specifies the length in bytes of the operand to be

transferred. The operand may be one, two, or four bytes in length; other length values

cause the main processor to initiate protocol violation exception processing.

If DR = 0, the main processor transfers the operand from the active system stack to the

operand CIR. The implied effective address mode used for the transfer is the (A7)+

addressing mode. A one-byte operand causes the stack pointer to be incremented by two

after the transfer to maintain word alignment of the stack.

If DR = 1, the main processor transfers the operand from the operand CIR to the active

system stack. The implied effective address mode used for the transfer is the –(A7)

addressing mode. A one-byte operand causes the stack pointer to be decremented by two

before the transfer to maintain word alignment of the stack.

7.4.13 Transfer Single Main Processor Register Primitive

The transfer single main processor register primitive transfers an operand between one of

the main processor's data or address registers and the coprocessor. This primitive applies

to general and conditional category instructions. Figure 7-33 shows the format of the

transfer single main processor register primitive.

The transfer single main processor register primitive uses the CA, PC, and DR bits as

described in 7.4.2 Coprocessor Response Primitive General Format. If the

coprocessor issues this primitive with CA = 0 during a conditional category instruction, the

main processor initiates protocol violation exception processing.

MOTOROLA

Figure 7-33. Transfer Single Main Processor Register Primitive Format

15

CA

15

CA

Figure 7-32. Transfer to/from Top of Stack Primitive Format

PC

PC

14

14

DR

DR

13

13

12

12

Freescale Semiconductor, Inc.

0

0

For More Information On This Product,

11

11

1

1

10

10

1

1

Go to: www.freescale.com

M68020 USER’S MANUAL

9

1

9

0

8

8

0

0

7

7

0

6

0

5

0

4

LENGTH

0

D/A

3

2

REGISTER

0

0

7- 41

Related parts for MC68020RC16E

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

(MC600 Series) INTEGRATED CIRCUITS

Manufacturer:

ETC

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: