MC7447AHX1420LB Freescale Semiconductor, MC7447AHX1420LB Datasheet - Page 40

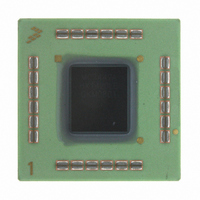

MC7447AHX1420LB

Manufacturer Part Number

MC7447AHX1420LB

Description

IC MPU RISC 1420MHZ 360-FCCBGA

Manufacturer

Freescale Semiconductor

Datasheet

1.MC7447AVS733NB.pdf

(56 pages)

Specifications of MC7447AHX1420LB

Processor Type

MPC74xx PowerPC 32-Bit

Speed

1.42GHz

Voltage

1.3V

Mounting Type

Surface Mount

Package / Case

360-FCCBGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Features

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC7447AHX1420LB

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

System Design Information

During inactive periods on the bus, the address and transfer attributes may not be driven by any master and

may, therefore, float in the high-impedance state for relatively long periods of time. Because the

MPC7447A must continually monitor these signals for snooping, this float condition may cause excessive

power draw by the input receivers on the MPC7447A or by other receivers in the system. These signals

can be pulled up through weak (10-KΩ) pull-up resistors by the system, address bus driven mode enabled

(see the MPC7450 RISC Microprocessor Family Users’ Manual for more information on this mode), or

they may be otherwise driven by the system during inactive periods of the bus to avoid this additional

power draw. Preliminary studies have shown the additional power draw by the MPC7447A input receivers

to be negligible and, in any event, none of these measures are necessary for proper device operation. The

snooped address and transfer attribute inputs are: A[0:35], AP[0:4], TT[0:4], CI, WT, and GBL.

If address or data parity is not used by the system, and respective parity checking is disabled through HID1,

the input receivers for those pins are disabled and do not require pull-up resistors, and may be left

unconnected by the system. If extended addressing is not used (HID0[XAEN] = 0), A[0:3] are unused and

must be pulled low to GND through weak pull-down resistors; additionally, if address parity checking is

enabled (HID1[EBA] = 1) and extended addressing is not used, AP[0] must be pulled up to OV

through

DD

a weak pull-up resistor. If the MPC7447A is in 60x bus mode, DTI[0:3] must be pulled low to GND

through weak pull-down resistors.

The data bus input receivers are normally turned off when no read operation is in progress and, therefore,

do not require pull-up resistors on the bus. Other data bus receivers in the system, however, may require

pull-ups, or that those signals be otherwise driven by the system during inactive periods. The data bus

signals are: D[0:63] and DP[0:7].

9.7

JTAG Configuration Signals

Boundary-scan testing is enabled through the JTAG interface signals. The TRST signal is optional in the

IEEE 1149.1 specification but is provided on all processors that implement the PowerPC architecture.

While it is possible to force the TAP controller to the reset state using only the TCK and TMS signals, more

reliable power-on reset performance will be obtained if the TRST signal is asserted during power-on reset.

Because the JTAG interface is also used for accessing the common on-chip processor (COP) function,

simply tying TRST to HRESET is not practical.

The COP function of these processors allows a remote computer system (typically a PC with dedicated

hardware and debugging software) to access and control the internal operations of the processor. The COP

interface connects primarily through the JTAG port of the processor, with some additional status

monitoring signals. The COP port requires the ability to independently assert HRESET or TRST in order

to fully control the processor. If the target system has independent reset sources, such as voltage monitors,

watchdog timers, power supply failures, or push-button switches, then the COP reset signals must be

merged into these signals with logic.

The arrangement shown in

Figure 19

allows the COP port to independently assert HRESET or TRST,

while ensuring that the target can drive HRESET as well. If the JTAG interface and COP header will not

be used, TRST should be tied to HRESET through a 0-Ω isolation resistor so that it is asserted when the

system reset signal (HRESET) is asserted, ensuring that the JTAG scan chain is initialized during

power-on. Although Freescale recommends that the COP header be designed into the system as shown in

Figure

19, if this is not possible, the isolation resistor will allow future access to TRST in the case where

a JTAG interface may need to be wired onto the system in debug situations.

MPC7447A RISC Microprocessor Hardware Specifications, Rev. 5

40

Freescale Semiconductor