EP1S80F1508C6 Altera, EP1S80F1508C6 Datasheet - Page 128

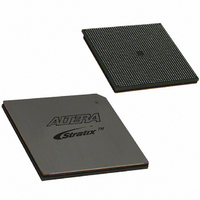

EP1S80F1508C6

Manufacturer Part Number

EP1S80F1508C6

Description

IC STRATIX FPGA 80K LE 1508-FBGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F780C7.pdf

(276 pages)

Specifications of EP1S80F1508C6

Number Of Logic Elements/cells

79040

Number Of Labs/clbs

7904

Total Ram Bits

7427520

Number Of I /o

1203

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

1508-FBGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Other names

544-1441

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP1S80F1508C6

Manufacturer:

ALTERA

Quantity:

465

Part Number:

EP1S80F1508C6

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

Company:

Part Number:

EP1S80F1508C6N

Manufacturer:

ALTERA

Quantity:

5

Part Number:

EP1S80F1508C6N

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

I/O Structure

Figure 2–67. Stratix IOE in DDR Output I/O Configuration

Notes to

(1)

(2)

2–114

Stratix Device Handbook, Volume 1

Column or Row

Interconnect

All input signals to the IOE can be inverted at the IOE.

The tristate is by default active high. It can, however, be designed to be active low.

I/O Interconnect

Figure

[15..0]

IOE_CLK[7..0]

2–67:

clkout

aclr/prn

sclr

Chip-Wide Reset

Register Delay

Register Delay

Logic Array

Enable Clock

Enable Delay

Enable Delay

Logic Array

Output Clock

to Output

to Output

Output

Output Register

Output Register

OE Register

OE Register

ENA

Notes

D

CLRN/PRN

D

CLRN/PRN

D

CLRN/PRN

D

CLRN/PRN

ENA

ENA

ENA

Q

Q

Q

Q

(1),

(2)

Drive Strength Control

Used for

DDR SDRAM

Pin Delay

Output

Open-Drain Output

Slew Control

clk

t

ZX

Output

Delay

OE Register

t

CO

Delay

V

CCIO

Altera Corporation

V

CCIO

Optional

PCI Clamp

Bus-Hold

Circuit

Programmable

Pull-Up

Resistor

July 2005