EP2AGX95EF29I5N Altera, EP2AGX95EF29I5N Datasheet - Page 41

EP2AGX95EF29I5N

Manufacturer Part Number

EP2AGX95EF29I5N

Description

IC ARRIA II GX FPGA 95K 780FBGA

Manufacturer

Altera

Series

Arria II GXr

Datasheets

1.EP2AGX45CU17C6N.pdf

(96 pages)

2.EP2AGX45CU17C6N.pdf

(14 pages)

3.EP2AGX45CU17C6N.pdf

(692 pages)

4.EP2AGX45CU17C6N.pdf

(10 pages)

5.EP2AGX45CU17C6N.pdf

(88 pages)

6.EP2AGX95EF29I5N.pdf

(306 pages)

Specifications of EP2AGX95EF29I5N

Number Of Logic Elements/cells

89178

Number Of Labs/clbs

3747

Total Ram Bits

6679

Number Of I /o

372

Voltage - Supply

0.87 V ~ 0.93 V

Mounting Type

Surface Mount

Operating Temperature

-40°C ~ 100°C

Package / Case

780-FBGA

Family Name

Arria® II GX

Number Of Logic Blocks/elements

93674

# I/os (max)

372

Frequency (max)

500MHz

Operating Supply Voltage (typ)

900mV

Logic Cells

93674

Ram Bits

7025459.2

Operating Supply Voltage (min)

0.87V

Operating Supply Voltage (max)

0.93V

Operating Temp Range

-40C to 100C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

780

Package Type

FC-FBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Lead Free Status / Rohs Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Chapter 1: Device Datasheet for Arria II Devices

Switching Characteristics

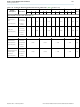

Table 1–35. Transceiver Specifications for Arria II GZ Devices (Part 6 of 6)

December 2010 Altera Corporation

Digital reset pulse width

Notes to

(1) The 3× speed grade is the fastest speed grade offered in the following Arria II GZ devices: EP2AGZ225, EP2AGZ300, and EP2AGZ350.

(2) The minimum reconfig_clk frequency is 2.5 MHz if the transceiver channel is configured in Transmitter only mode. The minimum

(3) The device cannot tolerate prolonged operation at this absolute maximum.

(4) You must use the 1.1-V RX V

(5) The rate matcher supports only up to

(6) Time taken to rx_pll_locked goes high from rx_analogreset de-assertion. Refer to

(7) Time for which the CDR must be kept in lock-to-reference mode after rx_pll_locked goes high and before rx_locktodata is asserted in

(8) Time taken to recover valid data after the rx_locktodata signal is asserted in manual mode. Refer to

(9) Time taken to recover valid data after the rx_freqlocked signal goes high in automatic mode. Refer to

(10) A GPLL may be required to meet the PMA-FPGA fabric interface timing above certain data rates. For more information, refer to the

(11) The Quartus II software automatically selects the appropriate slew rate depending on the configured data rate or functional mode.

(12) The Quartus II software automatically selects the appropriate /L divider depending on the configured data.

(13) If your design uses more than one dynamic reconfiguration controller (altgx_reconfig) instances to control the transceiver (altgx)

(14) The differential eye opening specification at the receiver input pins assumes that Receiver Equalization is disabled. If you enable Receiver

(15) The rise and fall time transition is specified from 20% to 80%.

reconfig_clk frequency is 37.5 MHz if the transceiver channel is configured in Receiver only or Receiver and Transmitter mode.

manual mode. Refer to

Clocking for Arria II Devices

channels physically located on the same side of the device AND if you use different reconfig_clk sources for these altgx_reconfig

instances, the delta time between any two of these reconfig_clk sources becoming stable must not exceed the maximum specification listed.

Equalization, the receiver circuitry can tolerate a lower minimum eye opening, depending on the equalization level. Use H-Spice simulation to

derive the minimum eye opening requirement with Receiver Equalization enabled.

Description

Table

Symbol/

1–34:

Figure 1–1 on page

chapter.

ICM

setting if the input serial data standard is LVDS.

Conditions

±

300 ppm.

—

1–34.

Min

–C3 and –I3

Typ

Minimum is two parallel clock cycles

Arria II Device Handbook Volume 3: Device Datasheet and Addendum

(1)

Max

Figure 1–1 on page

Min

Figure 1–1 on page

Figure 1–2 on page

–C4 and –I4

1–34.

Typ

Max

1–34.

1–34.

Transceiver

Unit

—

1–33