EP2AGX45DF29I5 Altera, EP2AGX45DF29I5 Datasheet - Page 66

EP2AGX45DF29I5

Manufacturer Part Number

EP2AGX45DF29I5

Description

IC ARRIA II GX FPGA 45K 780FBGA

Manufacturer

Altera

Series

Arria II GXr

Datasheets

1.EP2AGX45CU17C6N.pdf

(96 pages)

2.EP2AGX45CU17C6N.pdf

(14 pages)

3.EP2AGX45CU17C6N.pdf

(692 pages)

4.EP2AGX45CU17C6N.pdf

(10 pages)

5.EP2AGX45CU17C6N.pdf

(88 pages)

Specifications of EP2AGX45DF29I5

Number Of Logic Elements/cells

42959

Number Of Labs/clbs

1805

Total Ram Bits

3435

Number Of I /o

364

Voltage - Supply

0.87 V ~ 0.93 V

Mounting Type

Surface Mount

Operating Temperature

-40°C ~ 100°C

Package / Case

780-FBGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP2AGX45DF29I5N

Manufacturer:

ALTERA

Quantity:

201

Company:

Part Number:

EP2AGX45DF29I5N

Manufacturer:

ALTERA

Quantity:

853

1–58

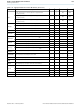

Table 1–44. PLL Specifications for Arria II GX Devices (Part 1 of 3)

Arria II Device Handbook Volume 3: Device Datasheet and Addendum

f

f

f

f

f

t

IN

INPFD

VCO

INDUTY

EINDUTY

INCCJ

(4)

Symbol

(3),

Core Performance Specifications for the Arria II Device Family

Input clock frequency (from clock input pins residing in

right/top/bottom banks) (–4 Speed Grade)

Input clock frequency (from clock input pins residing in

right/top/bottom banks) (–5 Speed Grade)

Input clock frequency (from clock input pins residing in

right/top/bottom banks) (–6 Speed Grade)

Input frequency to the PFD

PLL VCO operating Range

Input clock duty cycle

External feedback clock input duty cycle

Input clock cycle-to-cycle jitter (Frequency 100 MHz)

Input clock cycle-to-cycle jitter (Frequency 100 MHz)

This section describes the clock tree, phase-locked loop (PLL), digital signal

processing (DSP), embedded memory, configuration, and JTAG specifications for

Arria II GX and GZ devices.

Clock Tree Specifications

Table 1–42

Table 1–42. Clock Tree Performance for Arria II GX Devices

Table 1–43

Table 1–43. Clock Tree Performance for Arria II GZ Devices

PLL Specifications

Table 1–44

GCLK and RCLK

GCLK and RCLK

Clock Network

Clock Network

PCLK

PCLK

lists the clock tree specifications for Arria II GX devices.

lists the clock tree specifications for Arria II GZ devices.

lists the PLL specifications for Arria II GX devices.

Description

(2)

I3, C4

500

420

–C3 and –I3

700

500

Performance

Performance

C5,I5

500

350

Min

600

40

40

—

—

Chapter 1: Device Datasheet for Arria II Devices

5

5

5

5

–C4 and –I4

Typ

—

—

—

—

—

—

—

—

—

500

450

December 2010 Altera Corporation

400

280

C6

670

622

500

1,400

±750

Max

0.15

325

60

60

Switching Characteristics

(1)

(1)

(1)

ps (p–p)

UI (p–p)

Unit

MHz

MHz

MHz

MHz

MHz

MHz

MHz

Unit

MHz

MHz

Unit

%

%