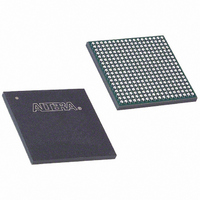

EP1C12F324C6 Altera, EP1C12F324C6 Datasheet - Page 11

EP1C12F324C6

Manufacturer Part Number

EP1C12F324C6

Description

IC CYCLONE FPGA 12K LE 324-FBGA

Manufacturer

Altera

Series

Cyclone®r

Datasheet

1.EP1C3T144C8.pdf

(106 pages)

Specifications of EP1C12F324C6

Number Of Logic Elements/cells

12060

Number Of Labs/clbs

1206

Total Ram Bits

239616

Number Of I /o

249

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

324-FBGA

Family Name

Cyclone®

Number Of Logic Blocks/elements

12060

# I/os (max)

249

Frequency (max)

405.2MHz

Process Technology

0.13um (CMOS)

Operating Supply Voltage (typ)

1.5V

Logic Cells

12060

Ram Bits

239616

Operating Supply Voltage (min)

1.425V

Operating Supply Voltage (max)

1.575V

Operating Temp Range

0C to 85C

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

324

Package Type

FBGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Lead Free Status / Rohs Status

Not Compliant

Other names

544-1034

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP1C12F324C6

Manufacturer:

ALTERA

Quantity:

7

Company:

Part Number:

EP1C12F324C6

Manufacturer:

ALTERA

Quantity:

1 831

Company:

Part Number:

EP1C12F324C6

Manufacturer:

ALTERA

Quantity:

210

Company:

Part Number:

EP1C12F324C6AA

Manufacturer:

ALTERA

Quantity:

3 000

Company:

Part Number:

EP1C12F324C6N

Manufacturer:

ALTERA

Quantity:

5

Figure 2–4. LAB-Wide Control Signals

Logic Elements

Altera Corporation

May 2008

Dedicated

LAB Row

Clocks

Local

Interconnect

Local

Interconnect

Local

Interconnect

Local

Interconnect

Local

Interconnect

Local

Interconnect

6

With the LAB-wide addnsub control signal, a single LE can implement a

one-bit adder and subtractor. This saves LE resources and improves

performance for logic functions such as DSP correlators and signed

multipliers that alternate between addition and subtraction depending

on data.

The LAB row clocks [5..0] and LAB local interconnect generate the

LAB-wide control signals. The MultiTrack

skew allows clock and control signal distribution in addition to data.

Figure 2–4

The smallest unit of logic in the Cyclone architecture, the LE, is compact

and provides advanced features with efficient logic utilization. Each LE

contains a four-input LUT, which is a function generator that can

implement any function of four variables. In addition, each LE contains a

programmable register and carry chain with carry select capability. A

single LE also supports dynamic single bit addition or subtraction mode

selectable by a LAB-wide control signal. Each LE drives all types of

interconnects: local, row, column, LUT chain, register chain, and direct

link interconnects. See

labclk1

labclkena1

shows the LAB control signal generation circuit.

labclk2

Figure

labclkena2

2–5.

asyncload

or labpre

syncload

TM

interconnect's inherent low

labclr1

labclr2

Logic Elements

synclr

Preliminary

addnsub

2–5