AD7879-1ACPZ-RL Analog Devices Inc, AD7879-1ACPZ-RL Datasheet - Page 33

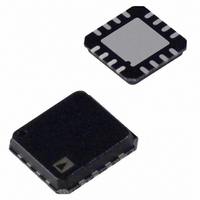

AD7879-1ACPZ-RL

Manufacturer Part Number

AD7879-1ACPZ-RL

Description

IC ADC 12BIT CTLR TOUCH 16LFCSP

Manufacturer

Analog Devices Inc

Type

Resistiver

Specifications of AD7879-1ACPZ-RL

Resolution (bits)

12 b

Data Interface

I²C, Serial

Touch Panel Interface

4-Wire

Number Of Inputs/keys

1 TSC

Data Rate/sampling Rate (sps, Bps)

105k

Voltage Reference

External

Voltage - Supply

1.6 V ~ 3.6 V

Current - Supply

10nA

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

16-LFCSP

Voltage Supply Source

Single Supply

Sampling Rate (per Second)

105k

Sampling Rate

105kSPS

Supply Voltage Range - Analog

1.6V To 3.6V

Supply Current

480µA

Digital Ic Case Style

CSP

No. Of Pins

16

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

SCL

Reading Data

A read transaction begins when the master writes the command

word to the AD7879/AD7889 with the read/write bit set to 1. The

master then supplies 16 clock pulses per data-word to be read,

and the AD7879/AD7889 clock out data from the addressed

register on the DOUT line. The first data-word is clocked out

on the first falling edge of SCL following the command word,

as shown in Figure 41.

DIN

CS

NOTES

1. MULTIPLE SEQUENTIAL REGISTERS CAN BE LOADED CONTINUOUSLY.

2. THE FIRST (LOWEST ADDRESS) REGISTER ADDRESS IS WRITTEN, FOLLOWED BY MULTIPLE 16-BIT DATA-WORDS.

3. THE ADDRESS AUTOMATICALLY INCREMENTS WITH EACH 16-BIT DATA-WORD (ALL 16 BITS MUST BE WRITTEN).

4. CS IS HELD LOW UNTIL THE LAST DESIRED REGISTER HAS BEEN LOADED.

5. 16-BIT COMMAND WORD SETTINGS FOR SEQUENTIAL WRITE OPERATION:

CW

CW[15:11] = 11100 (ENABLE WORD)

CW[10] = 0 (R/W)

CW[9:0] = [AD9, AD8, AD7, AD6, AD5, AD4, AD3, AD2, AD1, AD0] (STARTING MSB JUSTIFIED REGISTER ADDRESS)

15

DOUT

1

SCL

DIN

CS

ENABLE WORD

CW

14

2

CW

13

NOTES

1. DATA BITS ARE LATCHED ON SCL RISING EDGES. SCL CAN IDLE HIGH OR LOW BETWEEN WRITE OPERATIONS.

2. THE 16-BIT COMMAND WORD MUST BE WRITTEN ON DIN: 5 BITS FOR ENABLE WORD, 1 BIT FOR R/W, AND 10 BITS FOR REGISTER ADDRESS.

3. THE REGISTER DATA IS READ BACK ON THE DOUT PIN.

4. X DENOTES DON’T CARE.

5. XXX DENOTES HIGH IMPEDANCE THREE-STATE OUTPUT.

6. CS IS HELD LOW UNTIL ALL REGISTER BITS HAVE BEEN READ BACK.

7. 16-BIT COMMAND WORD SETTINGS FOR SINGLE READBACK OPERATION:

3

CW[15:11] = 11100 (ENABLE WORD)

CW[10] = 1 (R/W)

CW[9:0] = [AD9, AD8, AD7, AD6, AD5, AD4, AD3, AD2, AD1, AD0] (10-BIT MSB JUSTIFIED REGISTER ADDRESS)

CW

XXX

15

t

CW

2

12

1

t

1

4

ENABLE WORD

XXX

CW

14

CW

11

2

5

t

3

XXX

CW

13

R/W

CW

10

3

16-BIT COMMAND WORD

6

XXX

CW

12

CW

4

9

7

XXX

CW

11

CW

5

8

8

R/W

CW

XXX

t

10

4

STARTING REGISTER ADDRESS

CW

6

7

16-BIT COMMAND WORD

9

XXX

CW

9

CW

7

6

10

XXX

CW

Figure 40. Sequential Register Write, SPI Timing

Figure 41. Single Register Readback, SPI Timing

8

CW

8

5

11

CW

XXX

7

t

CW

5

9

4

12

REGISTER ADDRESS

XXX

CW

6

10

CW

3

Rev. C | Page 33 of 40

13

XXX

CW

5

11

CW

2

14

CW

XXX

4

12

CW

1

15

CW

XXX

3

13

CW

0

16

The AD7879/AD7889 continue to clock out data on the DOUT

line provided that the master continues to supply the clock signal

on SCL. The read transaction ends when the master takes CS high.

If the AD7879/AD7889 address pointer reaches its maximum

value, the AD7879/AD7889 repeatedly clock out data from the

addressed register. The address pointer does not wrap.

XXX

CW

2

14

D15

17

XXX

CW

1

15

DATA FOR STARTING

REGISTER ADDRESS

D14

18

XXX

CW

0

16

D15

X

17

t

6

D14

X

18

16-BIT READBACK DATA

D1

31

D13

X

19

D0

32

D15

33

D14

REGISTER ADDRESS

34

DATA FOR NEXT

D2

X

30

AD7879/AD7889

D1

X

t

8

31

t

7

D0

X

32

D1

47

XXX

D0

48

D15

49