XC6SLX16-2FTG256C Xilinx Inc, XC6SLX16-2FTG256C Datasheet - Page 38

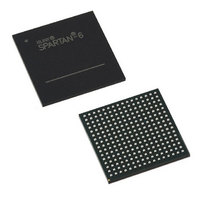

XC6SLX16-2FTG256C

Manufacturer Part Number

XC6SLX16-2FTG256C

Description

FPGA, SPARTAN-6 LX, 14K, 256FTGBGA

Manufacturer

Xilinx Inc

Series

Spartan® 6 LXr

Specifications of XC6SLX16-2FTG256C

No. Of Logic Blocks

2278

No. Of Macrocells

14579

Family Type

Spartan-6

No. Of Speed Grades

2

Total Ram Bits

589824

No. Of I/o's

186

Clock Management

DCM, PLL

I/o Supply Voltage

3.3V

Number Of Logic Elements/cells

14579

Number Of Labs/clbs

1139

Number Of I /o

186

Voltage - Supply

1.14 V ~ 1.26 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

256-LBGA

Package

256FTBGA

Family Name

Spartan®-6

Device Logic Cells

14579

Device Logic Units

9112

Number Of Registers

18224

Typical Operating Supply Voltage

1.2 V

Maximum Number Of User I/os

186

Ram Bits

589824

Core Supply Voltage Range

1.14V

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Other names

122-1672

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XC6SLX16-2FTG256C

Manufacturer:

TI

Quantity:

21 500

Company:

Part Number:

XC6SLX16-2FTG256C

Manufacturer:

Xilinx Inc

Quantity:

10 000

Input Serializer/Deserializer Switching Characteristics

Table 36: ISERDES2 Switching Characteristics

Output Serializer/Deserializer Switching Characteristics

Table 37: OSERDES2 Switching Characteristics

DS162 (v2.0) March 31, 2011

Preliminary Product Specification

Notes:

1.

Setup/Hold for Control Lines

T

T

Setup/Hold for Data Lines

T

T

T

T

T

Sequential Delays

T

F

Setup/Hold

T

T

T

T

Sequential Delays

T

T

F

ISCCK_BITSLIP

ISCCK_CE

ISDCK_D

ISDCK_DDLY

ISDCK_D_DDR

ISDCK_DDLY_DDR

ISCKD_DDLY_DDR

ISCKO_Q

CLKDIV

OSDCK_D

OSDCK_T

OSCCK_OCE

OSCCK_TCE

OSCKO_OQ

OSCKO_TQ

CLKDIV

T

OSDCK_T2

/T

/T

/T

/ T

Symbol

ISCKD_D

OSCKD_T

OSCKD_D

Symbol

/T

/T

/T

ISCKC_CE

/T

OSCKC_TCE

/ T

/T

OSCKC_OCE

ISCKD_DDLY

OSCKD_T2

ISCKD_D_DDR

ISCKC_BITSLIP

/

(1)

(T input setup/hold with respect to CLKDIV) are reported as T

D input Setup/Hold with respect to CLKDIV

T input Setup/Hold with respect to CLK

OCE input Setup/Hold with respect to CLK

TCE input Setup/Hold with respect to CLK

Clock to out from CLK to OQ

Clock to out from CLK to TQ

CLKDIV maximum frequency

BITSLIP pin Setup/Hold with respect to CLKDIV

CE pin Setup/Hold with respect to CLK

D pin Setup/Hold with respect to CLK

DDLY pin Setup/Hold with respect to CLK (using

IODELAY2)

D pin Setup/Hold with respect to CLK at DDR mode

D pin Setup/Hold with respect to CLK at DDR mode

(using IODELAY2)

CLKDIV to out at Q pin

CLKDIV maximum frequency

Description

Description

www.xilinx.com

Spartan-6 FPGA Data Sheet: DC and Switching Characteristics

OSDCK_T

/T

OSCKD_T

–0.03

–0.09

–0.47

–0.15

–0.25

–0.40

–0.03

–0.05

–0.03

–0.08

0.16

0.71

0.24

0.30

0.04

0.48

1.30

1.02

1.03

0.12

0.14

0.94

0.94

270

270

-3

-3

in TRACE report.

–0.09

–0.42

–0.05

–0.25

–0.03

–0.40

262.5

–0.05

–0.03

–0.08

262.5

–0.03

Speed Grade

Speed Grade

0.20

0.71

0.25

0.42

0.16

0.53

1.44

1.17

1.13

0.15

0.17

1.11

1.11

-3N

-3N

–0.09

–0.42

–0.05

–0.25

–0.03

–0.40

–0.03

–0.05

–0.03

–0.08

0.31

0.97

0.29

0.56

0.18

0.71

2.02

1.27

1.23

0.24

0.27

1.51

1.51

250

250

-2

-2

–0.14

–0.71

–0.05

–0.54

–0.05

–0.71

–0.02

–0.05

–0.17

–0.16

0.34

1.39

0.09

0.67

0.12

0.86

2.22

0.23

0.24

0.28

0.31

1.89

1.91

125

125

-1L

-1L

Units

Units

MHz

MHz

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

38