AD8152JBP Analog Devices Inc, AD8152JBP Datasheet - Page 17

AD8152JBP

Manufacturer Part Number

AD8152JBP

Description

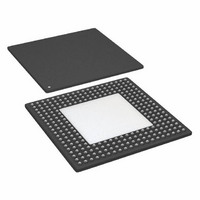

Digital Crosspoint 34 x 34 X-Point SW 3.2Gbps 256-Pin SBGA

Manufacturer

Analog Devices Inc

Datasheet

1.AD8152JBPZ.pdf

(32 pages)

Specifications of AD8152JBP

Package

256SBGA

Array Configuration

34x34

Number Of Arrays

1

Maximum Data Rate

3.2 Gbps

Power Supply Type

Single

Minimum Single Supply Voltage

2.25 V

Maximum Single Supply Voltage

3.63 V

Rohs Status

RoHS non-compliant

Function

Crosspoint Switch

Circuit

1 x 34:34

Voltage Supply Source

Single Supply

Voltage - Supply, Single/dual (±)

2.5 V ~ 3.3 V

Current - Supply

32mA

Operating Temperature

0°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

256-BGA Exposed Pad, 256-eBGA, 256-HBGA

Lead Free Status / RoHS Status

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AD8152JBP

Manufacturer:

ADI

Quantity:

170

Company:

Part Number:

AD8152JBP

Manufacturer:

Analog Devices Inc

Quantity:

10 000

Company:

Part Number:

AD8152JBPZ

Manufacturer:

ADI

Quantity:

642

Company:

Part Number:

AD8152JBPZ

Manufacturer:

Analog Devices Inc

Quantity:

10 000

CS Input

Chip select. This pin must be forced to logic low to program or

receive data from the logic interface, with the exception of the

RESET pin, described below. This pin has no effect on the signal

pairs and does not alter any of the stored control data.

RESET Input

Global output disable pin. Forcing the RESET pin to logic low

will disable all outputs, setting both ranks of all 34 input connec-

tion latches, regardless of the state of any other pins. This has the

effect of immediately disabling the 34 output signal pairs in the

matrix. The output level information is also changed. It is necessary

to momentarily hold RESET at a logic low state when powering

up the AD8152 in order to avoid random internal contention

where multiple inputs may be connected to one output. The

RESET pin is not gated by the state of the chip select pin, CS.

Control Interface Levels

The AD8152 control interface shares the data path supply pins,

VCC and VEE. The potential between the positive logic supply

VCC and the negative supply VEE must be at least 2.25 V and no

more than 3.63 V. Regardless of supply, the logic threshold is

approximately one-half the supply range, allowing the interface

to be used with most LVCMOS and LVTTL logic drivers.

Output Addressing

The AD8152 is programmed using a memory interface module,

with parallel address and data buses. Six bits (A5:A0) are used to

address the outputs. By setting the decimal value of these address

bits to a value from 0 to 33 inclusive, then one of the 34 outputs

is uniquely addressed.

One additional code, 63 (all 1s), is used for the broadcast mode.

If this address is selected, then all outputs will receive the same

programming. The remaining addresses in the space are not

valid and are reserved, Codes 34 to 66 inclusive. (See Table I.)

Connection and Output Current Programming

A seventh address bit (A6) determines which of two types of

programming is selected. If A6 = 0, connection matrix program-

ming is selected. If A6 = 1, output current programming is selected.

Using the Data Bus

Once it is determined which output is to be programmed (or broad-

cast to all outputs) and which type of programming (connection/

output-current), then the data bits (D5:D0) further define the

programming action.

If the selection is connection programming (A6 = 0), then the data

bits select the input that is to be connected to the addressed

output. If the broadcast address is selected, then the data bits select

the input that will be connected to all 34 outputs. (See Table II.)

A disable code (D5:D0 = 63, or all 1s) is used to disable (and

power down) the particular output that is addressed. A broadcast

disable can be effected by setting Code 63 on both the address

bus and the data bus along with A6 = 0.

Output-Current Programming

A current source in each output can be digitally programmed to

any one of 16 different current levels. Changing these current

levels will change the amplitude of the output swing that is

developed across the internal 50 W termination resistors.

To program the current for a particular output, its address is set on

A5:A0 (00–33), while A6 is set to 1. The four LSBs of the data

address (D3:D0) are then used to select one of the 16 output

current levels. D4 and D5 are “don’t cares” for output current

programming. (See Table III.)

REV. A

–17–

If it is desired to program all outputs to the same current level,

then the broadcast Code 63 can be placed on the address bus

(A5:A0), along with A6 = 1. (D3:D0) will then program all output

currents to the same level.

When the current code is set to 0000, a minimum current level

of 2 mA is obtained. For any other code, the current can be

calculated by (current code) ¥ 2 mA + 2 mA. Refer to Table III.

For example, 16 mA can be programmed by Code 0111. This is

7 ¥ 2 mA + 2 mA = 16 mA.

Register-Control Signals

Several single-ended logic input pins control the register loading

associated with the address and data buses described in the previ-

ous section. The control functions are tabulated in Table IV.

There are dual ranks of registers for the data that programs the

AD8152. The first rank registers accumulate the data for the

various outputs as they are being programmed one by one. The

second rank registers actually control the functions of the device.

The RESET signal is used to reset the connection matrix, disable

all outputs, and set all of the output currents to a default condition

at Code 0111. This action sets the output current to a nominal

value of 16 mA. The data in the first rank latches is also reset by

the assertion of RESET.

The CS signal is used to enable the control interface. If several

devices are used in a system with the other control signals

bussed, the CS signal can be used to select an individual device

to change its programming.

The WE signal is used to enable writing data to the first rank

registers. This data will not immediately affect the features of

the AD8152.

The UPDATE signal transfers the data from the first rank registers

to the second rank registers. After assertion of UPDATE, the

data actively controls the AD8152 functions.

The second rank registers can be read back through the data bus.

The output is addressed on A5:A0 and the connection/current is

selected via A6. Asserting RE will cause the second rank data to

appear on the data bus. The RE function will dominate over

WE if both are asserted at the same time. Broadcast readback is

not permitted.

Some typical programming waveforms for the control signals are

provided in Figure 6.

Input/Output Coupling

The AD8152 has internal 50 W termination resistors for each

single-ended input and output. This can also provide a 100 W

termination for a 100 W differential transmission line. All of the

input termination resistors connect to one common point called

VTTI. Similarly, each of the output termination resistors connects

to one common point called VTTO. The voltage can be set

independently at VTTI and VTTO to accommodate various

interface architectures.

UPDATE

A[6:0

D[5:0

WE

]

]

Figure 6. Programming Waveforms

VALID ADDRESS INPUT

VALID DATA INPUT

VALID ADDRESS INPUT

VALID DATA INPUT

AD8152