AD8152JBP Analog Devices Inc, AD8152JBP Datasheet - Page 15

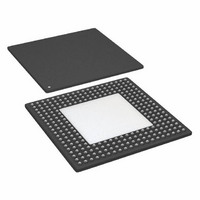

AD8152JBP

Manufacturer Part Number

AD8152JBP

Description

Digital Crosspoint 34 x 34 X-Point SW 3.2Gbps 256-Pin SBGA

Manufacturer

Analog Devices Inc

Datasheet

1.AD8152JBPZ.pdf

(32 pages)

Specifications of AD8152JBP

Package

256SBGA

Array Configuration

34x34

Number Of Arrays

1

Maximum Data Rate

3.2 Gbps

Power Supply Type

Single

Minimum Single Supply Voltage

2.25 V

Maximum Single Supply Voltage

3.63 V

Rohs Status

RoHS non-compliant

Function

Crosspoint Switch

Circuit

1 x 34:34

Voltage Supply Source

Single Supply

Voltage - Supply, Single/dual (±)

2.5 V ~ 3.3 V

Current - Supply

32mA

Operating Temperature

0°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

256-BGA Exposed Pad, 256-eBGA, 256-HBGA

Lead Free Status / RoHS Status

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AD8152JBP

Manufacturer:

ADI

Quantity:

170

Company:

Part Number:

AD8152JBP

Manufacturer:

Analog Devices Inc

Quantity:

10 000

Company:

Part Number:

AD8152JBPZ

Manufacturer:

ADI

Quantity:

642

Company:

Part Number:

AD8152JBPZ

Manufacturer:

Analog Devices Inc

Quantity:

10 000

Symbol

t

t

t

t

t

t

t

t

t

t

*Not shown

Symbol

t

t

t

t

t

REV. A

CSU

CHU

UOE

WOE

UOT

WOT

UOD

WOD

WHU

UW

CSR

CHR

RHA

RDE

AA

*

*

Setup Time

Hold Time

Output Enable Times

Output Toggle Times

Output Disable Times

Setup Time

Width of Update Pulse

Setup Time

Hold Time

Enable Time

Access Time

Parameter

OUT[0:33][N:P]

OUT[0:33][N:P]

DISABLING

OUTPUTS

ENABLING

Chip Select to Update

Chip Select from Update

Update to Output Enable

Write Enable to Output Enable

Update to Output Reprogram

Write Enable to Output Reprogram

Update to Output Disabled

Write Enable to Output Disabled

Write Enable to Update

Parameter

Chip Select to Read Enable

Chip Select from Read Enable

Address from Read Enable

Data from Read Enable

Data from Address

OUTPUTS

OUTPUTS

UPDATE

CS

RE

INPUT

D[5:0]

A[5:0]

Figure 4a. Transparent Write and Update Cycle

WE

CS

Figure 4b. Second Rank Readback Cycle

Table VIII. Second Rank Readback Cycle

Table VII. Transparent Update Cycle

INPUT {DATA 0}

t

CSR

t

CSU

ADDR 1

t

RDE

t

UOT

t

UOE

{ADDR 1}

DATA

–15–

INPUT {DATA 1}

INPUT {DATA 1}

t

UW

t

AA

ADDR 2

t

WOT

Conditions

T

VCC = 3.3 V

Conditions

T

VCC = 3.3 V

t

DATA {ADDR 2}

WOD

A

A

= 25 C

= 25 C

t

RHA

t

RDD

t

INPUT {DATA 2}

t

CHR

WHU

t

CHU

Min

0

0

5

Min

0

0

0

10

Typ

15

15

Typ

35

35

25

25

25

25

Max

30

Max

50

50

45

45

45

45

AD8152

Unit

ns

ns

ns

ns

ns

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns