MT9P031I12STM Aptina LLC, MT9P031I12STM Datasheet - Page 9

MT9P031I12STM

Manufacturer Part Number

MT9P031I12STM

Description

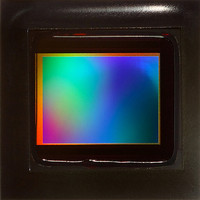

SENSOR IMAGE 5MP MONO CMOS 48LCC

Manufacturer

Aptina LLC

Type

CMOS Imagingr

Datasheets

1.MT9P031I12STCH_ES.pdf

(12 pages)

2.MT9P031I12STCH_ES.pdf

(2 pages)

3.MT9P031I12STM.pdf

(12 pages)

Specifications of MT9P031I12STM

Package / Case

48-iLCC

Pixel Size

2.2µm x 2.2µm

Active Pixel Array

2592H x 1944V

Frames Per Second

60

Voltage - Supply

2.6 V ~ 3.1 V

Supply Voltage Range

1.7V To 3.1V, 1.7V To 1.9V, 2.6V To 3.1V

Operating Temperature Range

-30°C To +70°C

Digital Ic Case Style

PLCC

No. Of Pins

48

Supply Voltage Max

3.1V

Ic Function

Digital Image Sensor

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

557-1430 - KIT HEAD BOARD FOR MT9P031557-1429 - KIT DEV FOR MT9P031

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Other names

557-1397

Q3884047

Q3956538

Q4007187

Q3884047

Q3956538

Q4007187

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MT9P031I12STM

Manufacturer:

ADI

Quantity:

119

Part Number:

MT9P031I12STM

Manufacturer:

APTINA

Quantity:

20 000

Company:

Part Number:

MT9P031I12STM-DP

Manufacturer:

ON

Quantity:

210

Company:

Part Number:

MT9P031I12STMD ES

Manufacturer:

Aptina LLC

Quantity:

135

Serial Bus Description

Sequence

PDF: 09005aef824c997f/Source: 09005aef824c998a

MT9T031_3100_PB_2.fm - Rev. A 8/06 EN

1. The master sends the write-node slave address and 8-bit address, just as in the write

2. The master sends a start bit and the read-mode slave address.

3. The master clocks out the register data 8 bits at a time.

4. The master sends an acknowledge bit after each 8-bit transfer.

5. The register address is auto-incremented after every 16 bits transferred.

6. The data transfer is stopped when the master sends a no-acknowledge bit.

Registers are written to and read from the MT9T031 through the two-wire serial inter-

face bus. The MT9T031 is a serial interface slave and is controlled by the serial clock

(SCLK), which is driven by the serial interface master. Data is transferred into and out of

the MT9T031 through the serial data (S

pull the S

allowed to pull the S

A typical read or write sequence begins with the master sending a start bit. After the start

bit, the master sends the slave device's 8-bit address. The last bit of the address deter-

mines if the request is a read or a write (“0” indicates a write and a “1” indicates a read).

The slave device acknowledges its address by sending an acknowledge bit back to the

master.

If the request was a write, the master then transfers the 8-bit register address to which a

write should take place. The slave sends an acknowledge bit to indicate that the register

address has been received. The master then transfers the data 8 bits at a time, with the

slave sending an acknowledge bit after each 8 bits.

The MT9T031 uses 16-bit data for its internal registers, thus requiring two 8-bit transfers

to write to one register. After 16 bits are transferred, the register address is automatically

incremented so that the next 16 bits are written to the next register address. The master

stops writing by sending a start or stop bit.

A typical read sequence is executed as follows:

request.

DATA

line down—the serial interface protocol determines which device is

DATA

line down at any given time.

MT9T031: 1/2-Inch 3-Mp Digital Image Sensor

8

Micron Technology, Inc., reserves the right to change products or specifications without notice.

DATA

) line. Either the slave or master device can

Serial Bus Description

©2006 Micron Technology, Inc. All rights reserved.