SI1141-A10-GMR Silicon Laboratories Inc, SI1141-A10-GMR Datasheet - Page 14

SI1141-A10-GMR

Manufacturer Part Number

SI1141-A10-GMR

Description

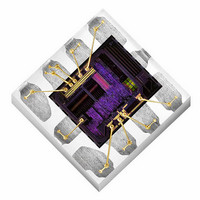

SENS IR PROXIMITY AMB LT 8-ODFN

Manufacturer

Silicon Laboratories Inc

Datasheet

1.SI1142-A10-GM.pdf

(70 pages)

Specifications of SI1141-A10-GMR

Mfg Application Notes

Si1141 Touchless Lavatory AppNote Si114x Designer's Guide AppNote Si114x Overlay Considerations AppNote Si1141 Cheek Detection in Smartphones C8051F990/Si1141 Smoke Detection AppNote Si114x irLED Guide AppNote Si114x Control Panel Guide AppNote

Output Type

Digital - I²C

Sensor Type

Proximity, Infrared and Ambient Light

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

336-1968

SI1141-A10-GM

SI1141-A10-GM

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

SI1141-A10-GMR

Manufacturer:

SILICON LABS/芯科

Quantity:

20 000

Si1141/42/43

encountered. An I

in preparation for an I

The I

master then continues to clock SCK to allow the Si1141/42/43 to drive the I

The Si1141/42/43 also supports burst reads and burst writes. The burst read is useful in collecting contiguous,

sequential registers. The Si1141/42/43 register map was designed to optimize for burst reads for interrupt

handlers, and the burst writes are designed to facilitate rapid programming of commonly used fields, such as

thresholds registers.

The internal register address is a six-bit (bit 5 to bit 0) plus an Autoincrement Disable (on bit 6). The Autoincrement

Disable is turned off by default. Disabling the autoincrementing feature allows the host to poll any single internal

register repeatedly without having to keep updating the Si1141/42/43 internal address every time the register is

read.

It is recommended that the host should read PS or ALS measurements (in the I

42/43 asserts INT. Although the host can read any of the Si1141/42/43's I

taken when reading 2-byte measurements outside the context of an interrupt handler. The host could be reading

part of the 2-byte measurement when the internal sequencer is updating that same measurement coincidentally.

When this happens, the host could be reading a hybrid 2-byte quantity whose high byte and low byte are parts of

different samples. If the host must read these 2-byte registers outside the context of an interrupt handler, the host

should “double-check” a measurement if the measurement deviates significantly from a previous reading.

14

SDA

SCL

2

C read access, like the I

START

2

C write access with only two bytes is typically used to set up the Si1141/42/43 internal address

2

C read.

SLA6

Slave Address + R/W

2

C write access, begins with a start or restart condition. In an I

SLA5-0

Figure 5. Host Interface Single Write

Figure 6. Host Interface Single Read

Figure 7. Host Interface Burst Write

Figure 8. Host Interface Burst Read

Figure 4. I

R/W

2

C Bit Timing Diagram

Rev. 1.1

ACK

D7

Data Byte

2

2

C with the internal register contents.

C registers at any time, care must be

2

C Register Map) when the Si1141/

D6-0

NACK

2

C read, the I

STOP

2

C