LH7A404N0F000B3,55 NXP Semiconductors, LH7A404N0F000B3,55 Datasheet - Page 48

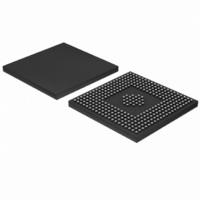

LH7A404N0F000B3,55

Manufacturer Part Number

LH7A404N0F000B3,55

Description

IC ARM9 BLUESTREAK MCU 324LFBGA

Manufacturer

NXP Semiconductors

Series

BlueStreak ; LH7Ar

Datasheet

1.LH7A404N0F000B355.pdf

(75 pages)

Specifications of LH7A404N0F000B3,55

Core Processor

ARM9

Core Size

16/32-Bit

Speed

200MHz

Connectivity

EBI/EMI, IrDA, Microwire, MMC, PS2, SmartCard, SPI, SSI, SSP, UART/USART, USB

Peripherals

AC'97, DMA, LCD, POR, PWM, WDT

Number Of I /o

64

Program Memory Type

ROMless

Ram Size

80K x 8

Voltage - Supply (vcc/vdd)

1.71 V ~ 3.6 V

Data Converters

A/D 9x10b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Package / Case

324-LFBGA

For Use With

568-4304 - BOARD EVAL FOR LH7A404

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Other names

568-4277

935285069551

LH7A404N0F000B3-S

935285069551

LH7A404N0F000B3-S

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LH7A404N0F000B3,55

Manufacturer:

NXP Semiconductors

Quantity:

10 000

LH7A404

SSP Waveforms

data frame formats:

• Texas Instruments SSI

• Motorola SPI

• National Semiconductor MICROWIRE

length, depending upon the programmed data size.

Each data frame is transmitted beginning with the

Most Significant Bit (MSB) i.e. ‘big endian’. For all

three formats, the SSP serial clock is held LOW (inac-

tive) while the SSP is idle. The SSP serial clock tran-

sitions only during active transmission of data. The

48

The Synchronous Serial Port (SSP) supports three

Each frame format is between 4 and 16 bits in

Figure 21. Texas Instruments Synchronous Serial Frame Format (Continuous Transfer)

Figure 20. Texas Instruments Synchronous Serial Frame Format (Single Transfer)

SSPTXD/

SSPTXD/

SSPFRM

SSPFRM

SSPRXD

SSPRXD

SSPCLK

SSPCLK

MSB

MSB

NXP Semiconductors

4 to 16 BITS

4 to 16 BITS

SSPFRM signal marks the beginning and end of a

frame.

synchronous serial frame format, Figure 22 through

Figure 29 show the Motorola SPI format, and Figure 30

and Figure 31 show National Semiconductor’s MICRO-

WIRE data frame format.

is pulsed prior to each frame’s transmission for one

serial clock period beginning at its rising edge. For this

frame format, both the SSP and the external slave

device drive their output data on the rising edge of the

clock and latch data from the other device on the falling

edge. See Figure 20 and Figure 21.

Figure 20 and Figure 21 show Texas Instruments

For Texas Instruments SSI format, the SSPFRM pin

LSB

LSB

32-Bit System-on-Chip

Preliminary data sheet

LH7A404-24

LH7A404-25