MC9S08GT60CFD Freescale Semiconductor, MC9S08GT60CFD Datasheet - Page 216

MC9S08GT60CFD

Manufacturer Part Number

MC9S08GT60CFD

Description

MCU 8BIT 60K FLASH 48-QFN

Manufacturer

Freescale Semiconductor

Series

HCS08r

Datasheet

1.M68EVB908GB60E.pdf

(290 pages)

Specifications of MC9S08GT60CFD

Core Processor

HCS08

Core Size

8-Bit

Speed

40MHz

Connectivity

I²C, SCI, SPI

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

39

Program Memory Size

60KB (60K x 8)

Program Memory Type

FLASH

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 3.6 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

48-QFN Exposed Pad

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC9S08GT60CFDE

Manufacturer:

ON

Quantity:

130

Company:

Part Number:

MC9S08GT60CFDE

Manufacturer:

FREESCALE

Quantity:

1 831

Part Number:

MC9S08GT60CFDE

Manufacturer:

FREESCALE

Quantity:

20 000

- Current page: 216 of 290

- Download datasheet (2Mb)

Inter-Integrated Circuit (IIC) Module

RSTA — Repeat START

13.5.4

TCF — Transfer Complete Flag

IAAS — Addressed as a Slave

BUSY — Bus Busy

ARBL — Arbitration Lost

216

Writing a one to this bit will generate a repeated START condition provided it is the current master.

This bit will always be read as a low. Attempting a repeat at the wrong time will result in loss of

arbitration.

This bit is set on the completion of a byte transfer. Note that this bit is only valid during or immediately

following a transfer to the IIC module or from the IIC module.The TCF bit is cleared by reading the

IIC1D register in receive mode or writing to the IIC1D in transmit mode.

The IAAS bit is set when its own specific address is matched with the calling address. Writing the

IIC1C register clears this bit.

The BUSY bit indicates the status of the bus regardless of slave or master mode. The BUSY bit is set

when a START signal is detected and cleared when a STOP signal is detected.

This bit is set by hardware when the arbitration procedure is lost. The ARBL bit must be cleared by

software, by writing a one to it.

1 = Transfer complete.

0 = Transfer in progress.

1 = Addressed as a slave.

0 = Not addressed.

1 = Bus is busy.

0 = Bus is idle.

1 = Loss of arbitration.

0 = Standard bus operation.

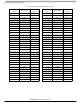

IIC Status Register (IIC1S)

Reset:

Read:

Write:

Bit 7

TCF

1

Figure 13-8. IIC Status Register (IIC1S)

= Unimplemented or Reserved

MC9S08GB/GT Data Sheet, Rev. 2.3

IAAS

6

0

BUSY

5

0

ARBL

4

0

3

0

0

SRW

2

0

IICIF

Freescale Semiconductor

1

0

RXAK

Bit 0

0

Related parts for MC9S08GT60CFD

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: