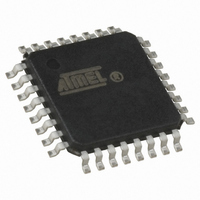

AT89LP428-20MH Atmel, AT89LP428-20MH Datasheet - Page 11

AT89LP428-20MH

Manufacturer Part Number

AT89LP428-20MH

Description

MCU 8051 4K FLASH SPI 32VQFN

Manufacturer

Atmel

Series

89LPr

Datasheet

1.AT89LP428-20AU.pdf

(149 pages)

Specifications of AT89LP428-20MH

Core Processor

8051

Core Size

8-Bit

Speed

20MHz

Connectivity

SPI, UART/USART

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Number Of I /o

30

Program Memory Size

4KB (4K x 8)

Program Memory Type

FLASH

Eeprom Size

512 x 8

Ram Size

768 x 8

Voltage - Supply (vcc/vdd)

2.4 V ~ 5.5 V

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

32-TQFP

Processor Series

AT89x

Core

8051

3rd Party Development Tools

PK51, CA51, A51, ULINK2

Development Tools By Supplier

AT89ISP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Data Converters

-

Lead Free Status / Rohs Status

Details

- Current page: 11 of 149

- Download datasheet (5Mb)

3.3

3.3.1

3654A–MICRO–8/09

External Data Memory

EDATA

AT89LP microcontrollers support a 16-bit external data memory address space. The external

memory space is accessed with the MOVX instructions. The AT89LP428/828 does not support

an external memory interface. However, some internal data memory resources are mapped into

portions of the external address space as shown in

require configuration before the CPU can access them. The AT89LP428/828 includes 512 bytes

of on-chip Extra RAM (EDATA) and 512/1024 bytes of nonvolatile Flash data memory (FDATA).

Figure 3-3.

The Extra RAM is a portion of the external memory space implemented as an internal 512-byte

auxiliary RAM. The Extra RAM is mapped into the EDATA space at the bottom of the external

memory address space, from 0000H to 01FFH. MOVX instructions to this address range will

access the internal Extra RAM. EDATA can be accessed with both 16-bit (MOVX @DPTR) and

8-bit (MOVX @Ri) addresses. When 8-bit addresses are used, the PAGE register (086H) sup-

plies the upper address bits. The PAGE register breaks EDATA into two 256-byte pages. A page

cannot be specified independently for MOVX @R0 and MOVX @R1. When 16-bit addresses are

used (DPTR), the IAP bit (MEMCON.7) must be zero to access EDATA. MOVX instructions to

EDATA require a minimum of 2 clock cycles.

Table 3-3.

Symbol

PAGE0

PAGE = 86H

Not Bit Addressable

Bit

03FF

01FF

0200

0000

Function

Selects which 256-byte page of EDATA is currently accessible by MOVX @Ri instructions.

External Data Memory Map

PAGE

–

7

– EDATA Page Register

AT89LP428

Flash Data

Extra RAM

(EDATA)

(FDATA)

–

6

–

5

–

4

–

3

Figure

05FF

01FF

0200

0000

3-3. These memory spaces may

Reset Value = XXXX XXX0B

–

2

AT89LP428/828

AT89LP828

Flash Data

Extra RAM

(FDATA)

(EDATA)

–

1

PAGE.0

0

11

Related parts for AT89LP428-20MH

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Atmel Corporation

Datasheet:

Part Number:

Description:

8-bit Microcontroller with 4K/8K Bytes In-System Programmable Flash

Manufacturer:

ATMEL [ATMEL Corporation]

Datasheet:

Part Number:

Description:

MCU 8051 4K FLASH SPI 32TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU 8051 4K FLASH SPI 28PDIP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU 8051 4K FLASH SPI 32PLCC

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

8-bit Microcontroller With 4k/8k Bytes In-system Programmable Flash

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet: