MCIMX515CJM6C Freescale Semiconductor, MCIMX515CJM6C Datasheet - Page 111

MCIMX515CJM6C

Manufacturer Part Number

MCIMX515CJM6C

Description

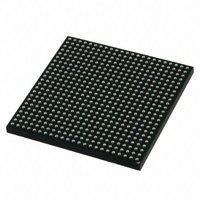

MULTIMEDIA PROC 529-LFBGA

Manufacturer

Freescale Semiconductor

Series

i.MX51r

Datasheets

1.MCIMX512DJM8C.pdf

(200 pages)

2.MCIMX515DJM8C.pdf

(2 pages)

3.MCIMX512CJM6C.pdf

(198 pages)

Specifications of MCIMX515CJM6C

Core Processor

ARM Cortex-A8

Core Size

32-Bit

Speed

600MHz

Connectivity

1-Wire, EBI/EMI, Ethernet, I²C, IrDA, MMC, SPI, SSI, UART/USART, USB OTG

Peripherals

DMA, I²S, LCD, POR, PWM, WDT

Number Of I /o

128

Program Memory Type

ROMless

Ram Size

128K x 8

Voltage - Supply (vcc/vdd)

0.8 V ~ 1.15 V

Oscillator Type

External

Operating Temperature

-20°C ~ 85°C

Package / Case

529-LFBGA

Processor Series

i.MX51

Core

ARM Cortex A8

Data Bus Width

32 bit

Program Memory Size

36 KB

Data Ram Size

128 KB

Interface Type

I2C, SPI, SSI, UART, USB

Maximum Clock Frequency

200 MHz

Number Of Timers

5

Operating Supply Voltage

0.8 V to 1.15 V

Maximum Operating Temperature

+ 95 C

Mounting Style

SMD/SMT

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

MCIMX51EVKJ

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MCIMX515CJM6C

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Part Number:

MCIMX515CJM6C

Manufacturer:

FREESCALE

Quantity:

20 000

Company:

Part Number:

MCIMX515CJM6CR2

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Freescale Semiconductor

4

5

6

7

8

9

DISP_RD_EN is predefined in REGISTER

10

chip-level output delay, board delays, a chip-level input delay, an IPU input delay. This value is chip specific.

11

CLK_OFFSET is predefined in REGISTER

12

DISP_RS_UP is predefined in REGISTER

13

DISP_RS_DOWN is predefined in REGISTER

14

DISP_CS_UP is predefined in REGISTER

Display interface clock down time for read

Display interface clock up time for read

Display interface clock down time for write

Display interface clock up time for write

This parameter is a requirement to the display connected to the IPU

Data read point

Display interface clock offset value

Loop back delay Tlbd is the cumulative propagation delay of read controls and read data. It includes an IPU output delay, a

Display RS up time

Display RS down time

Display RS up time

i.MX51 Applications Processors for Consumer and Industrial Products, Rev. 4

Tdicdw

Tdicdr

Tdicuw

Tdicur

Tdicdrs

Toclk

Tdrp

Tdicucs

Tdicurs

=

=

=

=

=

1

-- - T DI_CLK

2

=

1

-- - T DI_CLK

2

1

-- - T DI_CLK

2

⎛

⎝

=

1

-- - T DI_CLK

2

⎛

⎝

T DI_CLK

⎛

⎝

T

=

⎛

⎝

=

T DI_CLK

DI_CLK

T DI_CLK

T DI_CLK

×

×

×

×

×

ceil

×

×

ceil

ceil

ceil

×

×

ceil

ceil

ceil

ceil

ceil

---------------------------------------------- -

DI_CLK_PERIOD

DISP_READ_EN

2

---------------------------------------------------- -

DISP_CLK_OFFSET

------------------------------------------------------- -

2

---------------------------------------------------- -

DI_CLK_PERIOD

---------------------------------------------- -

DI_CLK_PERIOD

DISP_RS_DOWN_#

----------------------------------------------------- -

DI_CLK_PERIOD

---------------------------------------------- -

DI_CLK_PERIOD

DI_CLK_PERIOD

×

2

×

2

---------------------------------------------- -

DI_CLK_PERIOD

DI_CLK_PERIOD

---------------------------------------------- -

DI_CLK_PERIOD

DISP_RS_UP_#

DISP_CS_UP_#

DISP_DOWN_#

×

DISP_DOWN_#

×

DISP_UP_#

DISP_UP_#

⎞

⎠

⎞

⎠

⎞

⎠

⎞

⎠

Electrical Characteristics

111