LH7A400N0F000B5,55 NXP Semiconductors, LH7A400N0F000B5,55 Datasheet - Page 8

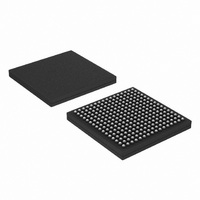

LH7A400N0F000B5,55

Manufacturer Part Number

LH7A400N0F000B5,55

Description

IC ARM9 BLUESTREAK MCU 256LFBGA

Manufacturer

NXP Semiconductors

Series

BlueStreak ; LH7Ar

Datasheet

1.LH7A400N0F000B555.pdf

(65 pages)

Specifications of LH7A400N0F000B5,55

Core Processor

ARM9

Core Size

16/32-Bit

Speed

200MHz

Connectivity

EBI/EMI, IrDA, Microwire, MMC, SmartCard, SPI, SSI, SSP, UART/USART, USB

Peripherals

AC'97, DMA, LCD, POR, PWM, WDT

Number Of I /o

60

Program Memory Type

ROMless

Ram Size

80K x 8

Voltage - Supply (vcc/vdd)

1.71 V ~ 3.6 V

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Package / Case

256-LFBGA

Processor Series

LH7A4

Core

ARM9TDMI

Data Bus Width

32 bit

Maximum Clock Frequency

14.7456 MHz

Operating Supply Voltage

3.3 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Lead Free Status / Rohs Status

Details

Other names

568-4274

935285073551

LH7A400N0F000B5-S

935285073551

LH7A400N0F000B5-S

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LH7A400N0F000B5,55

Manufacturer:

NXP Semiconductors

Quantity:

10 000

LH7A400

8

BGA

D13

C12

C11

E11

A12

PIN

M2

M4

A9

B9

D9

E9

K1

K2

K3

K5

N1

N2

N3

P1

P2

R1

K6

F9

L1

L2

L3

L4

L5

L7

L8

J5

LFBGA

A15

D11

E10

A13

B11

C11

PIN

M3

M5

C9

M1

M2

N1

N2

M4

R1

A9

B9

A8

K1

K2

K3

K4

K6

K5

L1

L2

L3

L5

P1

P2

P3

nSCS1

nSCS2

nSCS3

nSWE

nCAS

nRAS

DQM0

DQM1

DQM2

DQM3

PA0/LCDVD16

PA1/LCDVD17

PA2

PA3

PA4

PA5

PA6

PA7

PB0/

UARTRX1

PB1/UARTTX3

PB2/

UARTRX3

PB3/

UARTCTS3

PB4/

UARTDCD3

PB5/

UARTDSR3

PB6/SWID/

SMBD

PB7/

SMBCLK

PC0/

UARTTX1

PC1/LCDPS

PC2/

LCDVDDEN

PC3/LCDREV

PC4/

LCDSPS

SIGNAL

Sync Memory Chip Select 1

Sync Memory Chip Select 2

Sync Memory Chip Select 3

Sync Memory Write Enable

Sync Memory Column Address Strobe Signal

Sync Memory Row Address Strobe Signal

Sync Memory Data Mask 0

Sync Memory Data Mask 1

Sync Memory Data Mask 2

Sync Memory Data Mask 3

• GPIO Port A

• LCD Data bit 16. This CLCDC output signal is

• GPIO Port A

• LCD Data bit 17. This CLCDC output signal is

GPIO Port A

• GPIO Port B

• UART1 Receive Data Input

• GPIO Port B

• UART3 Transmit Data Out

• GPIO Port B

• UART3 Receive Data In

• GPIO Port B

• UART3 Clear to Send

• GPIO Port B

• UART3 Data Carrier Detect

• GPIO Port B

• UART3 Data Set Ready

• GPIO Port B

• Single Wire Data

• Smart Battery Data

• GPIO Port B

• Smart Battery Clock

• GPIO Port C

• UART1 Transmit Data Output

• GPIO Port C

• HR-TFT Power Save

• GPIO Port C

• HR-TFT Power Sequence Control

• GPIO Port C

• HR-TFT Gray Scale Voltage Reverse

• GPIO Port C

• HR-TFT Reset Row Driver Counter

always LOW.

always LOW.

Table 3. Functional Pin List (Cont’d)

DESCRIPTION

Rev. 01 — 16 July 2007

NXP Semiconductors

LOW: PC0

LOW: PC1

LOW: PC2

LOW: PC3

LOW: PC4

Input: PA0

Input: PA1

Input: PB0

Input: PB1

Input: PB2

Input: PB3

Input: PB4

Input: PB5

Input: PB6

Input: PB7

RESET

STATE

HIGH

HIGH

HIGH

HIGH

HIGH

HIGH

HIGH

HIGH

HIGH

HIGH

Input

UART3CON

No Change

No Change

No Change

No Change

No Change

No Change

No Change

No Change

No Change

No Change

No Change

No Change

No Change

No Change

No Change

No Change

No Change

No Change

No Change

No Change

No Change

No Change

No Change

No Change

No Change

No Change

STANDBY

= 1 (bit 3);

PINMUX:

otherwise

STATE

LOW if

32-Bit System-on-Chip

Preliminary data sheet

OUTPUT

DRIVE

12 mA

12 mA

12 mA

12 mA

12 mA

12 mA

12 mA

12 mA

12 mA

12 mA

12 mA

12 mA

12 mA

12 mA

12 mA

8 mA

8 mA

8 mA

8 mA

8 mA

8 mA

8 mA

8 mA

8 mA

8 mA

8 mA

I/O NOTES

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

O

O

O

O

O

O

O

O

O

7