EPF10K10 ETC, EPF10K10 Datasheet - Page 117

EPF10K10

Manufacturer Part Number

EPF10K10

Description

EMBEDDED PROGRAMMABLE LOGIC FAMILY

Manufacturer

ETC

Datasheet

1.EPF10K10.pdf

(138 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EPF10K100A3NBC356

Manufacturer:

ALTERA

Quantity:

21

Company:

Part Number:

EPF10K100ABC356-1

Manufacturer:

ALTERA

Quantity:

8 831

Company:

Part Number:

EPF10K100ABC356-1

Manufacturer:

ALTERA30

Quantity:

205

Company:

Part Number:

EPF10K100ABC356-1N

Manufacturer:

ST

Quantity:

230

Altera Corporation

Notes to tables:

(1)

(2)

(3)

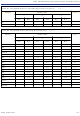

ClockLock &

ClockBoost

Timing

Parameters

t

t

t

t

t

INSUBIDIR

INHBIDIR

OUTCOBIDIR

XZBIDIR

ZXBIDIR

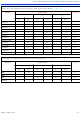

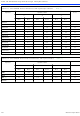

Table 113. EPF10K250A Device External Bidirectional Timing Parameters

All timing parameters are described in

Using an LE to register the signal may provide a lower setup time.

This parameter is specified by characterization.

Symbol

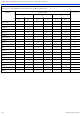

For the ClockLock and ClockBoost circuitry to function properly, the

incoming clock must meet certain requirements. If these specifications are

not met, the circuitry may not lock onto the incoming clock, which

generates an erroneous clock within the device. The clock generated by

the ClockLock and ClockBoost circuitry must also meet certain

specifications. If the incoming clock meets these requirements during

configuration, the ClockLock and ClockBoost circuitry will lock onto the

clock during configuration. The circuit will be ready for use immediately

after configuration. Figure 31 illustrates the incoming and generated clock

specifications.

Figure 31. Specifications for the Incoming & Generated Clocks

Min

9.3

0.0

2.0

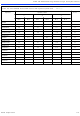

The t

nominal output clock period.

ClockLock-

Generated

Clock

I

-1

parameter refers to the nominal input clock period; the t

Input

Clock

Tables 32

Max

10.8

10.8

8.0

FLEX 10K Embedded Programmable Logic Family Data Sheet

t

R

through

t

OUTDUTY

t

CLK1

t

F

10.6

Min

0.0

2.0

Speed Grade

38

in this data sheet.

t

INDUTY

t

-2

O

t

I

12.2

12.2

Max

t

8.9

t

I

O +

t

INCLKSTB

t

JITTER

t

12.7

O –

Min

Note (1)

2.0

0.0

t

JITTER

O

-3

parameter refers to the

t

I

f

CLKDEV

10.4

14.2

14.2

Max

Unit

ns

ns

ns

ns

ns

117