lm2633mtd National Semiconductor Corporation, lm2633mtd Datasheet

lm2633mtd

Related parts for lm2633mtd

lm2633mtd Summary of contents

Page 1

... The input voltage for the switching channels ranges from 5V to 30V, which makes possible the choice of different battery chemistries and options. SpeedStep ™ trademark of Intel Corporation. © 2001 National Semiconductor Corporation Features GENERAL n Three regulated output voltages n 4.5V to 30V input range n Power good function ...

Page 2

... Connection Diagram TOP VIEW 48-Lead TSSOP (MTD) Order Number LM2633MTD See NS Package Number MTD48 Pin Descriptions FB1 (Pin 1):The feedback input for Channel 1. Connect to the load directly. COMP1 (Pin 2): Channel 1 compensation network connec- tion (connected to the output of the voltage error amplifier). ...

Page 3

3 www.national.com ...

Page 4

www.national.com 4 ...

Page 5

5 www.national.com ...

Page 6

Note 1: ’ =1’ means at least one variable is high. Note 2: ’Fault’ is the logic OR of UVLO and thermal shutdown. Note 3: ’Cap’ means the pin has a capacitor ...

Page 7

TABLE 3. VID Code and DAC Output (Continued) VID4 VID3 ...

Page 8

Absolute Maximum Ratings If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications. Voltages from the indicated pins to GND/PGND: VIN, KS1, KS2, SW1, SW2 ILIM1, ILIM2 VID0-VID4 VLIN, VDD1, VDD2, PGOOD ...

Page 9

Electrical Characteristics V = +15V unless otherwise indicated under the Conditions column. Typicals and limits appearing in plain type apply for +25˚C. Limits appearing in boldface type apply over 0˚C to +125˚C. J Symbol Parameter ...

Page 10

Electrical Characteristics V = +15V unless otherwise indicated under the Conditions column. Typicals and limits appearing in plain type apply for +25˚C. Limits appearing in boldface type apply over 0˚C to +125˚C. J Symbol Parameter ...

Page 11

Electrical Characteristics V = +15V unless otherwise indicated under the Conditions column. Typicals and limits appearing in plain type apply for +25˚C. Limits appearing in boldface type apply over 0˚C to +125˚C. J Symbol Parameter ...

Page 12

Electrical Characteristics V = +15V unless otherwise indicated under the Conditions column. Typicals and limits appearing in plain type apply for +25˚C. Limits appearing in boldface type apply over −40˚C to +125˚C. J Symbol Parameter ...

Page 13

Electrical Characteristics V = +15V unless otherwise indicated under the Conditions column. Typicals and limits appearing in plain type apply for +25˚C. Limits appearing in boldface type apply over −40˚C to +125˚C. J Symbol Parameter ...

Page 14

... Note 13: For detailed information on soldering plastic small-outline packages, refer to the Packaging Databook available from National Semiconductor Corporation. Note 14: Except for ILIM1 and ILIM2 pins, which are 1.5kV. For testing purposes, ESD was applied using the human-body model, a 100pF capacitor discharged through a 1 ...

Page 15

Electrical Characteristics Note 19: This parameter indicates how much current the LM2633 is drawing from the input supply when it is completely shut off. Note 20: When ON/SS1,2 pins are charged above this voltage, the under voltage protection feature is ...

Page 16

www.national.com 16 ...

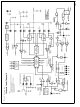

Page 17

Typical Application (Continued) TABLE 4. Bill of Materials for Typical Application Circuit ID Number C1 25SP56M Capacitor, OSCON C2 T510E108M004AS Capacitor, Tantalum C3 T510E108M004AS Capacitor, Tantalum C4 VJ1206S105MXJAC Capacitor, Ceramic C5 VJ1206S105MXJAC Capacitor, Ceramic C6 VJ0805Y104MXAAB Capacitor, Ceramic C7 VJ0805Y153MXJAB ...

Page 18

Typical Performance Characteristics Efficiency vs Load Current (Ch1, Typical Application) Efficiency vs Load Current (Ch2, Typical Application, FPWM = 1) PWM Frequency vs Temperature www.national.com Efficiency vs Load Current (Ch2, Typical Application, FPWM = 0) 200008A1 Switching Frequency vs Load ...

Page 19

Typical Performance Characteristics VLIN5 Voltage vs Temperature Current Sourcing Capability of Pin G3 vs Its Voltage Bias Current of Pin ILMx vs Temperature (Continued) Ch2 Reference Voltage vs Temperature 200008B5 DAC Voltage vs Temperature (Ch 1) 200008A6 (Typical Application, Ch ...

Page 20

Typical Performance Characteristics Skip-Mode Operation (Typical Application Load = 120 mA) Soft Start Under No Load ( Typical Application) Current Limit and UVP www.national.com (Continued) Soft Start with Constant Load Current 200008B3 ( Typical ...

Page 21

Typical Performance Characteristics Loop Bode Plot (Ch1, Typical Application, VIN = 8V, VOUT1 = 1.6V, No Load, Compensation: C14 = 390pF 100k, C15 = 150pF, R10 = 8.2k) Loop Bode Plot (Ch2, Typical Application, VIN = 8V, No ...

Page 22

Operation Descriptions General The LM2633 is a combination of three voltage regulator controllers. Among them, two are switching regulator control- lers and one is a linear regulator controller. The two switch- ing controllers, Channel 1 and Channel 2, operate 180˚ ...

Page 23

Operation Descriptions FET current. Once the bottom FET current flows from drain to source, the bottom FET will be turned off. This prevents negative inductor current. In force-PWM operation, the in- ductor current is allowed to go negative, so the ...

Page 24

Operation Descriptions output voltage will not be affected unless the UVLO method is used to release the latch. If the linear channel causes a UVP event, then the IC enters Shut Down Latch State . If later the fault at ...

Page 25

Design Procedures (Continued) ESR - Equivalent Series Resistance. Loading transient - a load transient when the load current goes from minimum load to full load. Unloading transient - a load transient when the load current goes from full load to ...

Page 26

Output Capacitor Selection (Continued) FIGURE 3. Load Transient Spec. Violation Because the response speed of the regulator is slow com- pared to a typical CPU load transient, the regulator has to rely heavily on the output capacitors to handle the ...

Page 27

Output Capacitor Selection (Continued) Maximum ESR calculation No matter how much capacitance there is, if the total com- bined ESR is not less than a certain value, the load transient requirement will not be met. The maximum allowed total combined ...

Page 28

Output Inductor Selection be a good idea to adjust the inductance value so that a requirement of 3.2 capacitors can be reduced to 3 capaci- tors. Inductor ripple current is often the criterion for selecting an output inductor. However, in ...

Page 29

Current Limit Setting What is actually monitored and limited is the peak drain- source voltage of the top FET when it is conducting. The equation for current limit resistor is as follows: where I is the desired load current limit ...

Page 30

Input Capacitor Selection FIGURE 6. Input Ripple RMS Current Ratio: 2-phase vs. In-phase Control Loop Design Samll Signal Model The buck regulator small signal model is shown in Figure 7 . The model is obtained by applying the current-controlled PWM ...

Page 31

Control Loop Design (Continued) Where D’ = 1−D • • the correction ramp slope the on-time slope of the e n current sense waveform, V ...

Page 32

Control Loop Design The value of f can be determined by comparing the denomi- p nators of Equation (35) and Equation (27) . The result is: From the above expressions, it can be seen that the control-output transfer function has ...

Page 33

Control Loop Design (Continued) TABLE 5. R1 and R2 Values vs. VID VID4:0 V (V) R DAC 1 00000 2.00 25k 00001 1.95 25k 00010 1.90 25k 00011 1.85 25k 00100 1.80 25k 00101 1.75 25k 00110 1.70 25k 00111 ...

Page 34

Control Loop Design Back to the previous example. Let then 5.1 x 310Hz = 1581Hz c_o The corresponding Bode plots of the compensation network and the loop transfer function are ...

Page 35

Control Loop Design (Continued) FIGURE 15. How Control-Output Transfer Function Changes with Q Values When Q is higher than 0.5, there will be a double-pole at half the switching frequency f . When Q is lower than 0.5, the n ...

Page 36

Control Loop Design amplifier, and I is the current drawn by the FB2 pin. The fb2 V and I have a typical value of 1.24V and 18 nA fb2 fb2 respectively. Example 1.5V ...

Page 37

Control Loop Design (Continued) If aluminum, tantalum or OSCON capacitors are going to be used, make sure the combined ESR is not greater than 10 Depending on the application, a different priority may be assigned to the selection ...

Page 38

Control Loop Design where V is equal to the reference voltage connected to the fb3 non-inverting input of the error amplifier and has a typical value of 1.24V, and I is the bias current drawn by the FB3 fb3 pin ...

Page 39

PCB Layout Guidelines 11. VLIN5 pin decoupling capacitor should be connected to the local analog ground. 12. Compensation components should be placed close to the IC, within centimeters. 13. Channel 3 should use the analog ground, not ...

Page 40

... National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications. inches (millimeters) 48-Lead TSSOP Package Order Number LM2633MTD NS Package Number MTD48 2. A critical component is any component of a life ...