EP1SGX25DF672C5N Altera, EP1SGX25DF672C5N Datasheet - Page 43

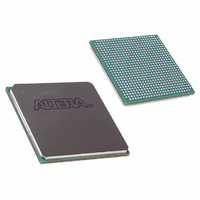

EP1SGX25DF672C5N

Manufacturer Part Number

EP1SGX25DF672C5N

Description

IC STRATIX GX FPGA 25K 672-FBGA

Manufacturer

Altera

Series

Stratix® GXr

Datasheet

1.EP1SGX10CF672C7N.pdf

(272 pages)

Specifications of EP1SGX25DF672C5N

Number Of Logic Elements/cells

25660

Number Of Labs/clbs

2566

Total Ram Bits

1944576

Number Of I /o

455

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

672-FBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP1SGX25DF672C5N

Manufacturer:

ALTERA

Quantity:

3 000

- Current page: 43 of 272

- Download datasheet (3Mb)

Altera Corporation

June 2006

The receiver PLL can also drive the fast regional, regional clocks, and

local routing adjacent to the associated transceiver block.

through

used by the recovered clock.

In the EP1SGX25 device, the receiver PLL recovered clocks from

transceiver blocks 0 and 1 drive RCLK[1..0] while transceiver blocks 2

and 3 drive RCLK[7..6]. The regional clocks feed logic in their

associated regions.

Figure 2–28. EP1SGX25 Receiver PLL Recovered Clock to Regional Clock

Connection

In addition, the receiver PLL’s recovered clocks can drive fast regional

lines (FCLK) as shown

in their associated regions.

2–31

show which fast regional and regional clock resource can be

Figure

2–29. The fast regional clocks can feed logic

PLD

Stratix GX Device Handbook, Volume 1

RCLK[11..10]

RCLK[9..8]

Transceiver Blocks

Stratix GX Transceivers

Stratix GX

Block 0

Block 1

Block 2

Block 3

Figures 2–28

2–33

Related parts for EP1SGX25DF672C5N

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Stratix Gx Device Family Data Sheet

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet: