EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 530

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

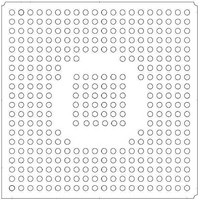

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 530 of 824

- Download datasheet (13Mb)

14

14-8

UART1 With HDLC and Modem Control Signals

EP93xx User’s Guide

14.2.3.4 UARTRTINTR

14.2.3.5 UARTINTR

14.3 Modem

14.4 HDLC

The transmit interrupt UARTTXINTR is not qualified with the UART Enable signal, which

allows operation in one of two ways. Data can be written to the transmit FIFO prior to

enabling the UART and the interrupts. Alternatively, the UART and interrupts can be enabled

so that data can be written to the transmit FIFO by an interrupt service routine.

This interrupt is connected to the system interrupt controller.

The receive timeout interrupt is asserted when the receive FIFO is not empty and no further

data is received over a 32-bit period. The receive timeout interrupt is cleared when the FIFO

becomes empty through reading all the data (or by reading the holding register).

This interrupt is not independently connected to the system interrupt controller.

The interrupts are also combined into a single output which is an OR function of the individual

masked sources. This output is connected to the system interrupt controller to provide

another level of masking on a individual peripheral basis. The combined UART interrupt is

asserted if any of the four individual interrupts above are asserted and enabled.

The modem hardware adds modem control signals RTSn, DTRn, and RI. Two modem

support registers provide a 16550 compatible modem control interface.

The HDLC receiver handles framing, address matching, CRC checking, control-octet

transparency or bit-stuffing, and optionally passes the CRC to the CPU at the end of the

packet. The HDLC transmitter handles framing, CRC generation, and control-octet

transparency or bit-stuffing. The CPU must assemble the frame in memory before

transmission. The HDLC receiver and transmitter use the UART FIFOs to buffer the data

streams.

When entering HDLC mode, always enable HDLC transmit and/or receive first by setting the

TXE and/or RXE bit in the UART1HDLCCtrl, and then enable the UART. When leaving HDLC

mode, disable the UART first, and then disable HDLC transmit and/or receive by clearing the

TXE and/or RXE bit. This insures that no bytes are sent by the UART transmitter without

proper HDLC framing, and that no bytes are received via the UART receiver without proper

HDLC decoding. In HDLC mode, the UART should be configured to use 8-bit characters and

no parity bit.

• If the FIFOs are disabled (have a depth of one location) and there is no data present in

the transmitters single location, the transmit FIFO is asserted HIGH. It is cleared by

performing a single write to the transmitter FIFO.

Copyright 2007 Cirrus Logic

DS785UM1

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc