EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 362

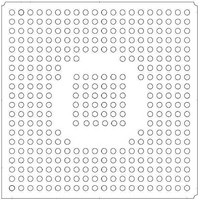

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 362 of 824

- Download datasheet (13Mb)

9

IntStsP/IntStsC

9-60

1/10/100 Mbps Ethernet LAN Controller

EP93xx User’s Guide

RSVD

31

15

Address:

Chip Reset:

Soft Reset:

Definition:

Bit Descriptions:

RSVD

RWI

30

14

RxMI

29

13

RxBI

MIII

28

12

0x8001_0028, for IntStsP - Read/Write

0x8001_002C, for IntStsC - Read Only

0x0000_0000

0x0000_0000

Interrupt Status Preserve and Clear Registers. The interrupt status bits are set

when the corresponding events occur in the MAC. If the corresponding

interrupt enable bit is set in the interrupt enable register, an interrupt signal will

be generated.

Interrupt status is available at two different offsets: Interrupt Status Preserve

and Interrupt Status Clear. Both offsets are a read of the same storage.

Reading the Interrupt Status register Preserve has no effect on the status in

the register, but writing a 1 to a location in this register clears the status bit,

writing a zero has no effect. Reading the Interrupt Status Clear register clears

all the bits in the register that are accessed as defined by the AHB HSIZE

signal. Therefore a routine which will handle all reported status may read via

the Interrupt Status Clear thereby saving a write operation.

RSVD:

RWI:

RxSQI

PHYSI

27

11

TxLEI

26

10

TI

Copyright 2007 Cirrus Logic

AHBE

ECI

25

9

Reserved. Unknown During Read.

Remote Wake-up Interrupt. The remote wake status is set

when a remote wake-up frame is received, and the

RemoteWakeEn (RXCtl) is set. A remote wake-up frame

must pass the receive destination address filter and have

a contiguous sequence of 6 bytes of FFh followed by 8

repetitions of the Individual Address and be a legal frame

(legal length and good CRC).

TxUHI

SWI

24

8

23

7

RSVD

22

6

RSVD

21

5

OTHER

20

4

TxSQ

19

3

RxSQ

MOI

18

2

TxCOI

17

1

DS785UM1

RSVD

RxROI

16

0

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc