MPC8360E-MDS-PBE Freescale Semiconductor, MPC8360E-MDS-PBE Datasheet - Page 7

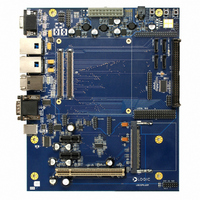

MPC8360E-MDS-PBE

Manufacturer Part Number

MPC8360E-MDS-PBE

Description

BOARD PROCESSOR FOR MPC8360E

Manufacturer

Freescale Semiconductor

Specifications of MPC8360E-MDS-PBE

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

3.1.1

3.1.2

System scalability is also made available through the number of UCCs and MCCs. The initial

implementation offers eight UCCs and one MCC; however as a result of the system-on-a-chip design

methodology used for the QUICC Engine, these numbers can be scaled to support an optimized mix of

communications channels. The flexible architecture of the QUICC Engine allows customers to customize

their own application protocol and filtering requirements, allowing Freescale to add more RISC engines

and/or UCCs on future family derivatives.

3.2

The QUICC Engine is a versatile communications complex that integrates several communications

peripheral controllers. It provides on-chip system design for a variety of applications, particularly in

communications and networking systems. The QUICC Engine has the following features:

Freescale Semiconductor

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

Seamless connection to PowerQUICC III family devices for increased control (CPU) application

processing requirements

ATM SAR up to 622 Mbps (OC-12) full duplex, with ATM traffic shaping (ATF TM4.1) for up to

64K ATM connections

Support for ATM AAL1 structured and unstructured circuit emulation service (CES 2.0)

Support for IMA and ATM transmission convergence sub-layer

ATM OAM handling features compatible with ITU-T I.610

PPP, multi-link (ML-PPP), multi-class (MC-PPP) and PPP multiplexing in accordance with the

following RFCs: 1661, 1662, 1990, 2686 and 3153

IP termination support for IPv4 and IPv6 packets including TOS, TTL, and header checksum

processing

L2 Ethernet switching using MAC address or IEEE 802.1P/Q VLAN tags

Support for ATM (AAL2/AAL5) to Ethernet (IP) interworking

Extensive support for ATM statistics and Ethernet RMON/MIB statistics.

Support for 256 channels or HDLC/transparent or 128 channels of SS#7

Support for two UL2 / POS-PHY interfaces with 124 multi-PHY addresses each.

Support for two 1000Mbps Ethernet interfaces using GMII or RGMII, TBI, RTBI.

Support for up to eight 10/100Mbps Ethernet interfaces using MII or RMII

Support for up to eight T1/E1/J1/E3 or DS-3 serial interfaces

Support for dual UART, I

Two 32-bit RISC controllers for flexible support of the communications peripherals

Serial DMA channel for receive and transmit on all serial channels

QUICC Engine

Protocols

Serial Interfaces

MPC8360E PowerQUICC II

2

Preliminary—Subject to Change Without Notice

C and SPI interfaces.

™

Pro Processor Product Brief, Rev. 0

Architecture Overview

7