EVAL-ADUC7020MKZ Analog Devices Inc, EVAL-ADUC7020MKZ Datasheet - Page 12

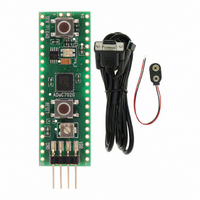

EVAL-ADUC7020MKZ

Manufacturer Part Number

EVAL-ADUC7020MKZ

Description

KIT MINI DEV FOR ADUC7026/7027

Manufacturer

Analog Devices Inc

Series

MiniKitr

Type

MCUr

Datasheet

1.USB-I2CLIN-CONV-Z.pdf

(96 pages)

Specifications of EVAL-ADUC7020MKZ

Contents

Mini-Board, Serial Cable, Software and Documentation

For Use With/related Products

ADuC7020

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 12 of 96

- Download datasheet (2Mb)

ADuC7019/20/21/22/24/25/26/27/28/29

Table 6. SPI Master Mode Timing (Phase Mode = 1)

Parameter

t

t

t

t

t

t

t

t

t

1

2

SL

SH

DAV

DSU

DHD

DF

DR

SR

SF

t

t

HCLK

UCLK

depends on the clock divider or CD bits in the PLLCON MMR. t

= 23.9 ns. It corresponds to the 41.78 MHz internal clock from the PLL before the clock divider; see Figure 57.

(POLARITY = 0)

(POLARITY = 1)

Description

SCLOCK low pulse width

SCLOCK high pulse width

Data output valid after SCLOCK edge

Data input setup time before SCLOCK edge

Data input hold time after SCLOCK edge

Data output fall time

Data output rise time

SCLOCK rise time

SCLOCK fall time

SCLOCK

SCLOCK

MOSI

MISO

1

t

1

DAV

t

SH

Figure 6. SPI Master Mode Timing (Phase Mode = 1)

t

DSU

MSB IN

HCLK

t

DHD

2

MSB

= t

t

SL

Rev. C | Page 12 of 96

2

UCLK

/2

t

DF

CD

; see Figure 57.

t

DR

BITS 6 TO 1

BITS 6 TO 1

Min

1 × t

2 × t

UCLK

UCLK

t

SR

Typ

(SPIDIV + 1) × t

(SPIDIV + 1) × t

5

5

5

5

LSB IN

t

SF

LSB

HCLK

HCLK

Max

25

12.5

12.5

12.5

12.5

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

Related parts for EVAL-ADUC7020MKZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC, ADJ LDO REG, 1.5V TO 5V 250mA MSOP-8

Manufacturer:

Vishay

Datasheet:

Part Number:

Description:

IC, ADJ LDO REG, 1.5V TO 5V 0.6A 8-TSSOP

Manufacturer:

Vishay

Datasheet:

Part Number:

Description:

IC, ADJ LDO REG, 1.5V TO 5V 250mA MSOP-8

Manufacturer:

Vishay

Datasheet:

Part Number:

Description:

IC ADJ LDO REG 1.5V TO 5V 150mA 5-SOT-23

Manufacturer:

Vishay

Datasheet:

Part Number:

Description:

BOARD EVAL AS1324-AD

Manufacturer:

austriamicrosystems

Datasheet:

Part Number:

Description:

IC, ADJ LDO REG, 1.5V TO 5V 0.6A 8-TSSOP

Manufacturer:

Vishay

Datasheet:

Part Number:

Description:

IC, ADJ LDO REG, 1.5V TO 5V, 0.3A, MSOP8

Manufacturer:

Vishay

Datasheet:

Part Number:

Description:

IC, ADJ LDO REG, 1.5V TO 5V, 0.3A, MSOP8

Manufacturer:

Vishay

Datasheet:

Part Number:

Description:

IC, ADJ LDO REG 1.215V TO 5V 0.3A MSOP-8

Manufacturer:

Vishay

Datasheet:

Part Number:

Description:

IC, ADJ LDO REG 1.215V TO 5V 0.3A MSOP-8

Manufacturer:

Vishay

Datasheet:

Part Number:

Description:

±1.7g Dual-Axis IMEMS Accelerometer Evaluation Board

Manufacturer:

Analog Devices Inc

Datasheet:

Part Number:

Description:

IC MULTIPLIER ANALOG 8-SOIC T/R

Manufacturer:

Analog Devices Inc

Datasheet:

Part Number:

Description:

IC ANALOG MULTIPLIER 8-DIP

Manufacturer:

Analog Devices Inc

Datasheet:

Part Number:

Description:

IC ANALOG MULTIPLIER 8-SOIC

Manufacturer:

Analog Devices Inc

Datasheet:

Part Number:

Description:

IC ANALOG MULTIPLIER 8-DIP

Manufacturer:

Analog Devices Inc

Datasheet: