KDC2708LEVAL Intersil, KDC2708LEVAL Datasheet - Page 14

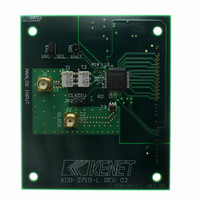

KDC2708LEVAL

Manufacturer Part Number

KDC2708LEVAL

Description

DAUGHTER CARD FOR KAD2708

Manufacturer

Intersil

Series

FemtoCharge™r

Datasheets

1.KAD2708L-35Q68.pdf

(16 pages)

2.KMB-001LEVALZ.pdf

(7 pages)

3.KDC5514EVALZ.pdf

(9 pages)

Specifications of KDC2708LEVAL

Number Of Adc's

1

Number Of Bits

8

Sampling Rate (per Second)

275M

Data Interface

Parallel

Inputs Per Adc

1 Differential

Input Range

1.5 Vpp

Power (typ) @ Conditions

275mW @ 275MSPS

Voltage Supply Source

Single Supply

Operating Temperature

-40°C ~ 85°C

Utilized Ic / Part

KAD2708L-27, KMB001 Motherboard

For Use With

KMB001LEVAL - MOTHERBOARD FOR LVDS ADC CARD

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Equivalent Circuits

IN P

IN N

10 0

9 5

9 0

8 5

8 0

7 5

7 0

6 5

6 0

5 5

5 0

1

AV D D 3

A VD D3

FIGURE 27. SNR vs CLOCK JITTER

tj=1 00 ps

FIGURE 28. ANALOG INPUTS

2pF

1 0

In put Fr equen cy - MH z

Φ

F 1

Φ

F 1

tj=10 p s

14

Φ

Φ

F 2

F 2

tj=1 ps

tj=0.1 ps

1 00

DATA

DATA

C sam p

C sam p

0.3pF

0.3pF

FIGURE 30. LVDS OUTPUTS

OVDD

1 0 Bits

14 Bits

12 Bits

Pipeline

Pipeline

C harge

C harge

To

To

KAD2708L

1 00 0

DATA

DATA

OVDD

Any internal aperture jitter combines with the input clock jitter

in a root-sum-square fashion, since they are not statistically

correlated, and this determines the total jitter in the system.

The total jitter, combined with other noise sources, then

determines the achievable SNR.

Digital Outputs

Data is output on a parallel bus with LVDS-compatible

drivers.

The output format (Binary or Two’s Complement) is selected

via the 2SC pin as shown in Table 3.

CLKN

CLKP

AVDD (or unconnected)

OVDD

AVDD2

AVDD2

2SC PIN

AVSS

D[7:0]P

D[7:0]N

TABLE 3. 2SC PIN SETTINGS

FIGURE 29. CLOCK INPUTS

Two’s Complement

AVDD2

MODE

Binary

April 14, 2011

Generation

To Clock

FN6813.1