DS34T101GN+ Maxim Integrated Products, DS34T101GN+ Datasheet - Page 8

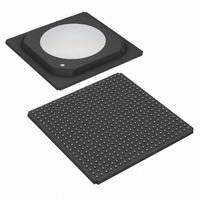

DS34T101GN+

Manufacturer Part Number

DS34T101GN+

Description

IC TDM OVER PACKET 484TEBGA

Manufacturer

Maxim Integrated Products

Type

TDM (Time Division Multiplexing)r

Datasheet

1.DS34T108GN.pdf

(16 pages)

Specifications of DS34T101GN+

Applications

Data Transport

Mounting Type

Surface Mount

Package / Case

484-BGA Exposed Pad, 484-eBGA, 484-HBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

5 Features

Global Features

Clock Synthesizers

Line Interface Units (LIUs)

____________________________________________________ DS34T101, DS34T102, DS34T104, DS34T108

TDMoP Interfaces

Ethernet Interface

End-to-end TDM synchronization through the IP/MPLS domain by on-chip, per-port TDM clock recovery

64 independent bundles/connections, each with its own:

Flexible on-chip cross-connection capability

Packet loss compensation and handling of misordered packets

Glueless SDRAM interface

Complies with MPLS-Frame Relay Alliance Implementation Agreements 4.1, 5.1 and 8.0

Complies with ITU-T standards Y.1413 and Y.1414.

Complies with Metro Ethernet Forum 3 and 8

Complies with IETF RFC 4553 (SAToP), RFC 5086 (CESoPSN) and RFC 5087 (TDMoIP)

IEEE 1146.1 JTAG boundary scan

1.8V and 3.3V Operation with 5.0V tolerant I/O

Clocks to operate LIUs, jitter attenuators, framers, BERTs and HDLC controllers can be synthesized from a

single clock input for both E1 and T1 operation (10MHz, 19.44MHz, 38.88MHz or 77.76MHz on the CLK_HIGH

pin or 1.544MHz or 2.048MHz on the MCLK pin)

Clocks to operate the TDMoP clock recovery machines can synthesized from a single clock input (10MHz,

19.44MHz, 38.88MHz or 77.76MHz on the CLK_HIGH pin)

Clock to operate TDMoP logic and SDRAM interface (50MHz or 75MHz) can be synthesized from a single

25MHz clock on the CLK_SYS pin

Receives E1, T1 and G.703 2048kHz synchronization signal

Fully software configurable including software-selectable internal Tx and Rx termination

Suitable for both short-haul and long-haul applications

Receive sensitivity options from (0dB to -12dB) to (0dB to -43dB) for E1 and to (0dB to -36dB) for T1

Receive signal level indication: 0dB to -37.5dB

Internal receive termination options for 75, 100, 110, and 120 lines

Receive monitor-mode gain settings of 14dB, 20dB, 26dB, and 32dB

Flexible transmit waveform generation

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

DS34T101: 1 E1/T1 LIU/Framer/TDMoP interface

DS34T102: 2 E1/T1 LIUs/Framers/TDMoP interfaces

DS34T104: 4 E1/T1 LIUs/Framers/TDMoP interfaces

DS34T108: 8 E1/T1 LIUs/Framers/TDMoP interfaces

All four devices: optionally 1 high-speed E3/DS3/STS-1 TDMoP interface

All four devices: each interface optionally configurable for serial operation for V.35 and RS530

One 10/100 Mbps port configurable for MII, RMII or SSMII interface format

Half or full duplex operation

VLAN support according to 802.1p and 802.1Q including stacked tags

Fully compatible with IEEE 802.3 standard

Transmit and receive queues

Configurable jitter-buffer depth

Connection-level redundancy, with traffic duplication option

Internal bundle cross-connect capability, with DS0 resolution

Any framer receiver port to any TDMoP block receive interface to maintain bundle connectivity

Any TDMoP block transmit interface to any framer transmit port to maintain bundle connectivity

8 of 16