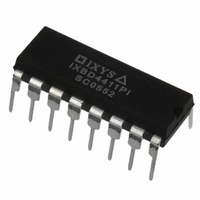

IXBD4411PI IXYS, IXBD4411PI Datasheet

IXBD4411PI

Specifications of IXBD4411PI

Related parts for IXBD4411PI

IXBD4411PI Summary of contents

Page 1

... ISOSMART Half Bridge Driver Chipset TM Type Description IXBD4410PI Full-Feature Low-Side Driver 16-Pin P-DIP IXBD4411PI Full-Feature High-Side Driver 16-Pin P-DIP IXBD4410SI Full-Feature Low-Side Driver 16-Pin SO IXBD4411SI Full-Feature High-Side Driver 16-Pin SO The IXBD4410/IXBD4411 ISOSMART chipset is designed to control the gates of two Power MOSFETs or Power ...

Page 2

... EE 600 -3 -4.8 Dimensions in inch (1" = 25.4 mm) 16-Pin SOIC V +0 °C °C °C °C K/W Die substrate K/W connected to tab 16-Pin Plastic DIP 1 µ Ω 4 Ω A End view V pF Ω kHz V © 2004 IXYS All rights reserved IXBD4410 IXBD4411 ...

Page 3

... Fault Output Delay for any Fault Conditions (4410/4411) t FLT Delay kΩ C FLT pu Overcurrent Protection Delay t Driver-Off delay time C oc Fig. 1a: IXBD4410/4411 Switching time test circuit © 2004 IXYS All rights reserved Characteristic Values = 25° unless otherwise specified) DD min. typ. 9.5 10.5 0.1 0.15 ...

Page 4

... The fault signal that is returned from Fig. 2: IXBD4411, high-side driver block diagram Fig. 3: IXBD4410, low-side driver block diagram Fig. 4: Logic representation of IXBD4410 FLT signal IXBD4410 IXBD4411 © 2004 IXYS All rights reserved ...

Page 5

... Miller capaci- tance or from inductive ground transients. These charge pumps provide -5 V relative to the local driver ground when © 2004 IXYS All rights reserved +15 V, and at rated average DD currents of 25 mA. The charge pump requires two external capacitors, C7 and C11 in Fig ...

Page 6

... IXBD4411, this output responds to the transmitted signal from the companion IXBD4410. A "high" at INH of the IXBD4410 drives will turn it on ("high"). A "low" will turn it off ("low"). This output will turn off ("low") also in response to any fault condition. © 2004 IXYS All rights reserved IXBD4410 IXBD4411 ...

Page 7

... Q1. This dv/dt is impressed across the Miller capacitance of Q1, forcing a large current to flow out the gate © 2004 IXYS All rights reserved Fig. 5: Switching a clamped inductive load terminal of the device. If this current pulse causes a high enough voltage ...

Page 8

... DC bus potential. To keep this normal condition from setting the internal fault flip-flop of the IXBD4410 or the IXBD4411, an internal CMOS switch is turned on and placed across lM and KG pins shorting them together. This effectively discharges C8 or C12 in Fig. 6 and maintains zero potential © 2004 IXYS All rights reserved R s ...

Page 9

... IXBD4410/4411 and its associated circuitry. © 2004 IXYS All rights reserved Fig. 8: Typical 3-phase motor control system block diagram PCB Layout Considerations The IXBD4410/4411 is intended to be used in high voltage, high speed, high dv/dt applications ...

Page 10

... AWG magnet wire are made. The two windings are segment wound to achieve primary-to- secondary isolation 2500 V~. The six-turn primaries are connected to the respective IXBD4410/4411 transmitter outputs and the two-turn secondaries are connected to their respective receiver inputs. © 2004 IXYS All rights reserved ...

Page 11

... The resistor will control the damping of the signal and limit the peak transmitter output current. The receiver is designed to operate © 2004 IXYS All rights reserved 6:2 Fig. 11: Ferrite bead dimensions 125 over a wide common mode input range. ...