IXDD408PI IXYS, IXDD408PI Datasheet - Page 9

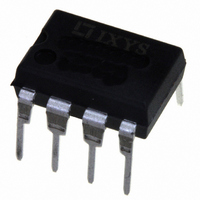

IXDD408PI

Manufacturer Part Number

IXDD408PI

Description

IC MOSFET DRIVER LS 8A SGL 8-DIP

Manufacturer

IXYS

Type

Low Side Gate Driverr

Datasheet

1.IXDD408PI.pdf

(10 pages)

Specifications of IXDD408PI

Configuration

Low-Side

Input Type

Non-Inverting

Delay Time

38ns

Current - Peak

8A

Number Of Configurations

1

Number Of Outputs

1

Voltage - Supply

4.5 V ~ 25 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Through Hole

Package / Case

8-DIP

Rise Time

18 ns

Fall Time

19 ns

Supply Voltage (min)

4.5 V

Supply Current

3 mA

Maximum Power Dissipation

975 mW

Maximum Operating Temperature

+ 85 C

Mounting Style

Through Hole

Minimum Operating Temperature

- 40 C

Number Of Drivers

1

Output Current

8 A

For Use With

EVDD408 - EVALUATION BOARD FOR IXDD408 DVR

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

High Side Voltage - Max (bootstrap)

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

IXDD 408PI

IXDD 408PI

IXDD 408PI

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

IXDD408PI

Manufacturer:

IXYS

Quantity:

877

Supply Bypassing and Grounding Practices,

Output Lead inductance

When designing a circuit to drive a high speed MOSFET

utilizing the IXDD408, it is very important to keep certain design

criteria in mind, in order to optimize performance of the driver.

Particular attention needs to be paid to Supply Bypassing,

Grounding, and minimizing the Output Lead Inductance.

Say, for example, we are using the IXDD408 to charge a

5000pF capacitive load from 0 to 25 volts in 25ns…

Using the formula: I= V C / t, where V=25V C=5000pF &

in 25ns will take a constant current of 5A. (In reality, the charging

current won’t be constant, and will peak somewhere around

8A).

SUPPLY BYPASSING

In order for our design to turn the load on properly, the IXDD408

must be able to draw this 5A of current from the power supply

in the 25ns. This means that there must be very low impedance

between the driver and the power supply. The most common

method of achieving this low impedance is to bypass the

power supply at the driver with a capacitance value that is a

magnitude larger than the load capacitance. Usually, this

would be achieved by placing two different types of bypassing

capacitors, with complementary impedance curves, very close

to the driver itself. (These capacitors should be carefully

selected, low inductance, low resistance, high-pulse current-

service capacitors). Lead lengths may radiate at high frequency

due to inductance, so care should be taken to keep the lengths

of the leads between these bypass capacitors and the IXDD408

to an absolute minimum.

GROUNDING

In order for the design to turn the load off properly, the IXDD408

must be able to drain this 5A of current into an adequate

grounding system. There are three paths for returning current

that need to be considered: Path #1 is between the IXDD408

and it’s load. Path #2 is between the IXDD408 and it’s power

supply. Path #3 is between the IXDD408 and whatever logic

is driving it. All three of these paths should be as low in

resistance and inductance as possible, and thus as short as

practical. In addition, every effort should be made to keep these

three ground paths distinctly separate.

instance), the returning ground current from the load may

develop a voltage that would have a detrimental effect on the

logic line driving the IXDD408.

OUTPUT LEAD INDUCTANCE

Of equal importance to Supply Bypassing and Grounding are

issues related to the Output Lead Inductance. Every effort

should be made to keep the leads between the driver and it’s

load as short and wide as possible. If the driver must be placed

farther than 2” from the load, then the output leads should be

treated as transmission lines. In this case, a twisted-pair

should be considered, and the return line of each twisted pair

should be placed as close as possible to the ground pin of the

driver, and connect directly to the ground terminal of the load.

t=25ns we can determine that to charge 5000pF to 25 volts

Otherwise, (for

9

TTL to High Voltage CMOS Level Translation

The enable (EN) input to the IXDD408 is a high voltage

CMOS logic level input where the EN input threshold is ½ V

and may not be compatible with 5V CMOS or TTL input levels.

The IXDD408 EN input was intentionally designed for

enhanced noise immunity with the high voltage CMOS logic

levels. In a typical gate driver application, V

EN input threshold at 7.5V, a 5V CMOS logical high input

applied to this typical IXDD408 application’s EN input will be

misinterpreted as a logical low, and may cause undesirable

or unexpected results. The note below is for optional

adaptation of TTL or 5V CMOS levels.

The circuit in Figure 28 alleviates this potential logic level

misinterpretation by translating a TTL or 5V CMOS logic input

to high voltage CMOS logic levels needed by the IXDD408 EN

input. From the figure, V

typically set between 8V to 20V, and V

supply, typically between 3.3V to 5.5V. Resistors R1 and R2

form a voltage divider network so that the Q1 base is

positioned at the midpoint of the expected TTL logic transition

levels.

the Q1 emitter will drive it on. This causes the level translator

output, the Q1 collector output to settle to V

V

interpreted as a high voltage CMOS logic low (<1/3V

V

A TTL high, V

V

Figure 28 will cause Q1 to be biased off. This results in Q1

collector being pulled up by R3 to V

high voltage CMOS logic high output. The high voltage CMOS

logical EN output applied to the IXDD408 EN input will enable

it, allowing the gate driver to fully function as an 8 Amp output

driver.

The total component cost of the circuit in Figure 28 is less

than $0.10 if purchased in quantities >1K pieces. It is

recommended that the physical placement of the level

translator circuit be placed close to the source of the TTL or

CMOS logic circuits to maximize noise rejection.

Figure 28 - TTL to High Voltage CMOS Level Translator

A TTL or 5V CMOS logic low, V

(From Gate Driver

(From Logic

Power Supply)

Power Supply)

TTLLOW

CC

5VCMOSHIGH

or

=15V given in the IXDD408 data sheet.)

TTL

=<~2V, which is sufficiently low to be correctly

V

Input)

CC

DD

=~>3.5V, applied to the EN input of the circuit in

IXDD408PI/408SI/408YI/408CI

TTLHIGH

=>~2.4V, or a 5V CMOS high,

3.3K

3.3K

CC

R1

R2

is the gate driver power supply,

10K

TTLLOW

R3

Q1

2N3904

CC

=~<0.8V, input applied to

=15V, and provides a

DD

is the logic power

CC

CESATQ1

=15V and the

(To IXDD408

Output

CMOS

High Voltage

EN Input)

+

CC

=5V for

EN

CC

,