X9521V20I-A Intersil, X9521V20I-A Datasheet - Page 4

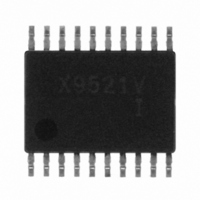

X9521V20I-A

Manufacturer Part Number

X9521V20I-A

Description

IC DCP DUAL EEPROM MEM 20-TSSOP

Manufacturer

Intersil

Type

Laser Diode Controller (Fiber Optic)r

Datasheet

1.X9521V20I.pdf

(24 pages)

Specifications of X9521V20I-A

Number Of Channels

2

Voltage - Supply

2.7 V ~ 5.5 V

Current - Supply

1.5mA

Operating Temperature

-40°C ~ 85°C

Package / Case

20-TSSOP

Mounting Type

Surface Mount

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

X9521V20I-AIS

DEVICE INTERNAL ADDRESSING

Addressing Protocol Overview

The user addressable internal components of the X9521

can be split up into three main parts:

—Two Digitally Controlled Potentiometers (DCPs)

—EEPROM array

—Control and Status (CONSTAT) Register

Depending upon the operation to be performed on each

of these individual parts, a 1, 2 or 3 Byte protocol is used.

All operations however must begin with the Slave

Address Byte being issued on the SDA pin. The Slave

address selects the part of the X9521 to be addressed,

and specifies if a Read or Write operation is to be per-

formed.

It should be noted that in order to perform a write opera-

tion to either a DCP or the EEPROM array, the Write

Enable Latch (WEL) bit must first be set (See “BL1, BL0:

Block Lock protection bits - (Nonvolatile)” on page 12.)

Slave Address Byte

Following a START condition, the master must output a

Slave Address Byte (Refer to Figure 4.). This byte con-

sists of three parts:

—The Device Type Identifier which consists of the most

significant four bits of the Slave Address (SA7 - SA4).

The Device Type Identifier must always be set to 1010

in order to select the X9521.

Data Output

Data Output

Transmitter

Receiver

Master

Master

from

from

from

from

SCL

SCL

Start

4

Figure 3.

Acknowledge Response From Receiver

1

X9521

—The next three bits (SA3 - SA1) are the Internal Device

—The Least Significant Bit of the Slave Address (SA0)

Address bits. Setting these bits to 000 internally

selects the EEPROM array, while setting these bits to

111 selects the DCP structures in the X9521. The

CONSTAT Register may be selected using the Inter-

nal Device Address 010.

Byte is the R/W bit. This bit defines the operation to be

performed on the device being addressed (as defined

in the bits SA3 - SA1). When the R/W bit is “1”, then a

READ operation is selected. A “0” selects a WRITE

operation (Refer to Figure 4.)

Figure 4.

SA7

1 0 1 0

Internal Address

DEVICE TYPE

(SA3 - SA1)

IDENTIFIER

8

Bit SA0

SA6

000

010

111

0

1

SA5

Slave Address Format

Acknowledge

SA4

9

SA3

Internally Addressed

CONSTAT Register

EEPROM Array

INTERNAL

ADDRESS

DEVICE

SA2

Operation

Device

WRITE

READ

DCP

SA1

September 21, 2010

READ /

WRITE

R/W

SA0

FN8207.2