M4-192/96-10VC Lattice, M4-192/96-10VC Datasheet - Page 5

M4-192/96-10VC

Manufacturer Part Number

M4-192/96-10VC

Description

CPLD - Complex Programmable Logic Devices Use ispMACH 4000V or M4A5

Manufacturer

Lattice

Datasheet

1.M4A5-19296-10VNI.pdf

(62 pages)

Specifications of M4-192/96-10VC

Product Category

CPLD - Complex Programmable Logic Devices

Memory Type

EEPROM

Number Of Macrocells

192

Maximum Operating Frequency

182 MHz

Delay Time

10 ns

Number Of Programmable I/os

96

Operating Supply Voltage

4.75 V to 5.25 V

Maximum Operating Temperature

+ 70 C

Minimum Operating Temperature

0 C

Package / Case

TQFP-144

Mounting Style

SMD/SMT

Number Of Product Terms Per Macro

20

Factory Pack Quantity

60

Supply Voltage - Max

5.25 V

Supply Voltage - Min

4.75 V

FUNCTIONAL DESCRIPTION

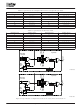

The fundamental architecture of ispMACH 4A devices (Figure 1) consists of multiple, optimized PAL

blocks interconnected by a central switch matrix. The central switch matrix allows communication between

PAL blocks and routes inputs to the PAL blocks. Together, the PAL blocks and central switch matrix allow

the logic designer to create large designs in a single device instead of having to use multiple devices.

The key to being able to make effective use of these devices lies in the interconnect schemes. In the

ispMACH 4A architecture, the macrocells are flexibly coupled to the product terms through the logic

allocator, and the I/O pins are flexibly coupled to the macrocells due to the output switch matrix. In

addition, more input routing options are provided by the input switch matrix. These resources provide the

flexibility needed to fit designs efficiently.

Notes:

1. 16 for ispMACH 4A devices with 1:1 macrocell-I/O cell ratio (see next page).

2. Block clocks do not go to I/O cells in M4A(3,5)-32/32.

3. M4A(3,5)-192, M4A(3,5)-256, M4A3-384, and M4A3-512 have dedicated clock pins which cannot be used as inputs and do not connect to the central switch

matrix.

Clock/Input

Dedicated

Note 3

Input Pins

Pins

Figure 1. ispMACH 4A Block Diagram and PAL Block Structure

33/

34/

36

Generator

Switch

Matrix

Clock

Logic

Array

Input

with XOR

Allocator

ispMACH 4A Family

Logic

16

4

16

PAL Block

PAL Block

Macrocells

Output/

Buried

16

Note 2

Note 1

16

8

PAL Block

17466G-001

Pins

Pins

Pins

I/O

I/O

I/O

®

5