nb3n106k ON Semiconductor, nb3n106k Datasheet

nb3n106k

Manufacturer Part Number

nb3n106k

Description

3.3v Differential 1 6 Fanout Clock And Data Driver With Hcsl Outputs

Manufacturer

ON Semiconductor

Datasheet

1.NB3N106K.pdf

(9 pages)

NB3N106K

3.3V Differential 1:6 Fanout

Clock and Data Driver with

HCSL Outputs

Description

with High−speed Current Steering Logic (HCSL) outputs optimized

for ultra low propagation delay variation. The NB3N106K is designed

with HCSL clock distribution and FBDIMM applications in mind.

signals per Figures 6, 7, and 8. Single−ended LVPECL, HCSL,

LVCMOS, or LVTTL levels are accepted with a proper external V

reference supply per Figures 4 and 9. Input pins incorporate separate

internal 50 W termination resistors allowing additional single ended

system interconnect flexibility.

IREF (Pin 1) to GND per Figure 5. Outputs can also interface to LVDS

receivers when terminated per Figure 10.

skew. Optimal design, layout, and processing minimize skew within a

device and from device to device. System designers can take

advantage of the NB3N106K’s performance to distribute low skew

clocks across the backplane or the motherboard.

Features

•

•

•

•

•

•

•

•

•

*For additional information on our Pb−Free strategy and soldering details, please

© Semiconductor Components Industries, LLC, 2011

November, 2011 − Rev. 4

download the ON Semiconductor Soldering and Mounting Techniques

Reference Manual, SOLDERRM/D.

The NB3N106K is a differential 1:6 Clock and Data fanout buffer

Inputs can directly accept differential LVPECL, LVDS, and HCSL

Output drive current is set by connecting a 475 W resistor from

The NB3N106K specifically guarantees low output–to–output

400 MHz

Typical Input Clock Frequency 100, 133, 166, 200, 266, 333, and

220 ps Typical Rise and Fall Times

800 ps Typical Propagation Delay

Dtpd 100 ps Maximum Propagation Delay Variation per Diff Pair

0.1 ps Typical RMS Additive Phase Jitter

Operating Range: V

Differential HCSL Output Levels

LVDS Output Levels with Interface Termination

These are Pb−Free Devices*

CC

=

3.0 V to 3.6 V with V

EE

=

0 V

1

th

See detailed ordering and shipping information in the package

dimensions section on page 8 of this data sheet.

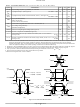

VTCLK

VTCLK

CLK

CLK

GND

Figure 1. Pin Configuration (Top View)

V

*For additional marking information, refer to

Application Note AND8002/D.

CC

A

L

Y

W

G

ORDERING INFORMATION

MARKING DIAGRAM*

http://onsemi.com

= Assembly Location

= Wafer Lot

= Year

= Work Week

= Pb−Free Package

ALYWG

NB3N

106K

G

Publication Order Number:

R

REF

MN SUFFIX

CASE 485L

QFN−24

NB3N106K/D

I

REF

Q0

Q0

Q1

Q1

Q4

Q4

Q5

Q5