S29JL064H90TAI00 Advanced Micro Devices, S29JL064H90TAI00 Datasheet

S29JL064H90TAI00

Available stocks

Related parts for S29JL064H90TAI00

S29JL064H90TAI00 Summary of contents

Page 1

S29JL064H 64 Megabit ( 8-Bit 16-Bit) CMOS 3.0 Volt-only, Simultaneous Read/Write Flash Memory Distinctive Characteristics Architectural Advantages Simultaneous Read/Write operations — Data can be continuously read from one bank while executing erase/program functions in another bank. ...

Page 2

General Description The S29JL064H megabit, 3.0 volt-only flash memory device, organized as 4,194,304 words of 16 bits each or 8,388,608 bytes of 8 bits each. Word mode data appears on DQ15–DQ0; byte mode data appears on DQ7–DQ0. ...

Page 3

DMS (Data Management Software) allows systems to easily take advantage of the advanced architecture of the simultaneous read/write product line by al- lowing removal of EEPROM devices. DMS will also allow the system software to be simplified will ...

Page 4

Table Of Contents Product Selector Guide . . . . . . . . . . . . . . . . . . . . . .5 Block Diagram . . . . . . . . . . ...

Page 5

Product Selector Guide Part Number Speed Option Standard Voltage Range: V Max Access Time (ns), t ACC CE# Access (ns OE# Access (ns Block Diagram Mux A21–A0 RY/BY# A21–A0 STATE RESET# CONTROL ...

Page 6

Connection Diagrams A15 1 A14 2 A13 3 A12 4 A11 5 A10 A19 9 A20 10 WE# 11 RESET# 12 A21 13 WP#/ACC 14 RY/BY# 15 A18 16 A17 ...

Page 7

Pin Description A21–A0 DQ14–DQ0 DQ15/A-1 CE# OE# WE# WP#/ACC RESET# BYTE# RY/BY Logic Symbol 22 A21–A0 DQ15–DQ0 (A-1) CE# OE# WE# WP#/ACC RESET# RY/BY# BYTE# April 28, 2004 S29JL064HA2 = 22 Addresses = 15 Data ...

Page 8

... S29JL064H55TAI00 S29JL064H55TFI00 S29JL064H55TFI00 S29JL064H60TAI00 S29JL064H60TAI00 S29JL064H60TFI00 S29JL064H60TFI00 S29JL064H70TAI00 S29JL064H70TAI00 S29JL064H70TFI00 S29JL064H70TFI00 S29JL064H90TAI00 S29JL064H90TAI00 S29JL064H90TFI00 S29JL064H90TFI00 S29JL064H70TAN00 S29JL064H70TAN00 S29JL064H70TFN00 S29JL064H70TFN00 S29JL064H90TAN00 S29JL064H90TAN00 S29JL064H90TFN00 S29JL064H90TFN00 Note:Listed TSOP part numbers describe products based on Copper (Cu) leadframes. Contact your local sales office for products based on Alloy-42 leadframes. ...

Page 9

Order Number Package Markings S29JL064H55BAI00 JL064H55BAI00 S29JL064H55BFI00 JL064H55BFI00 S29JL064H60BAI00 JL064H60BAI00 S29JL064H60BFI00 JL064H60BFI00 S29JL064H70BAI00 JL064H70BAI00 S29JL064H70BFI00 JL064H70BFI00 S29JL064H90BAI00 JL064H90BAI00 S29JL064H90BFI00 JL064H90BFI00 April 28, 2004 S29JL064HA2 Valid Combinations for BGA Packages Package Not Lead (Pb)- Free Lead (Pb)- Free Not Lead (Pb)- ...

Page 10

Device Bus Operations This section describes the requirements and use of the device bus operations, which are initiated through the internal command register. The command register itself does not occupy any addressable memory location. The register is a latch used ...

Page 11

Word/Byte Configuration The BYTE# pin controls whether the device data I/O pins operate in the byte or word configuration. If the BYTE# pin is set at logic ‘1’, the device is in word con- figuration, DQ15–DQ0 are active and controlled ...

Page 12

Accelerated Program Operation The device offers accelerated program operations through the ACC function. This is one of two functions provided by the WP#/ACC pin. This function is primarily intended to allow faster manufacturing throughput at the factory. If the system ...

Page 13

Standby Mode When the system is not reading or writing to the device, it can place the device in the standby mode. In this mode, current consumption is greatly reduced, and the outputs are placed in the high impedance state, ...

Page 14

Output Disable Mode When the OE# input are placed in the high impedance state output from the device is disabled. The output pins IH S29JL064H S29JL064HA2 April 28, 2004 ...

Page 15

Sector Address Bank Sector A21–A12 SA0 0000000000 SA1 0000000001 SA2 0000000010 SA3 0000000011 SA4 0000000100 SA5 0000000101 SA6 0000000110 SA7 0000000111 SA8 0000001xxx SA9 0000010xxx SA10 0000011xxx Bank 1 SA11 0000100xxx SA12 0000101xxx SA13 0000110xxx SA14 0000111xxx SA15 0001000xxx SA16 ...

Page 16

Table 2. S29JL064H Sector Architecture (Continued) Sector Address Bank Sector A21–A12 SA23 0010000xxx SA24 0010001xxx SA25 0010010xxx SA26 0010011xxx SA27 0010100xxx SA28 0010101xxx SA29 0010110xxx SA30 0010111xxx SA31 0011000xxx SA32 0011001xxx SA33 0011010xxx SA34 0011011xxx SA35 0011000xxx SA36 0011101xxx SA37 ...

Page 17

Table 2. S29JL064H Sector Architecture (Continued) Sector Address Bank Sector A21–A12 SA71 1000000xxx SA72 1000001xxx SA73 1000010xxx SA74 1000011xxx SA75 1000100xxx SA76 1000101xxx SA77 1000110xxx SA78 1000111xxx SA79 1001000xxx SA80 1001001xxx SA81 1001010xxx SA82 1001011xxx SA83 1001100xxx SA84 1001101xxx SA85 ...

Page 18

Table 2. S29JL064H Sector Architecture (Continued) Sector Address Bank Sector A21–A12 SA119 1110000xxx SA120 1110001xxx SA121 1110010xxx SA122 1110011xxx SA123 1110100xxx SA124 1110101xxx SA125 1110110xxx SA126 1110111xxx SA127 1111000xxx SA128 1111001xxx SA129 1111010xxx Bank 4 SA130 1111011xxx SA131 1111100xxx SA132 ...

Page 19

When using programming equipment, the autoselect mode requires dress pin A9. Address pins must be as shown in Table 5. In addition, when verifying sector protection, the sector address must appear on the appropriate highest order address bits (see Table ...

Page 20

Table 6. S29JL064H Boot Sector/Sector Block Addresses for Protection/Unprotection Sector A21–A12 SA0 0000000000 SA1 0000000001 SA2 0000000010 SA3 0000000011 SA4 0000000100 SA5 0000000101 SA6 0000000110 SA7 0000000111 0000001XXX, SA8–SA10 0000010XXX, 0000011XXX, SA11–SA14 00001XXXXX SA15–SA18 00010XXXXX SA19–SA22 00011XXXXX SA23–SA26 00100XXXXX SA27-SA30 ...

Page 21

Sector protect/Sector Unprotect requires V implemented either in-system or via programming equipment. the algorithms and unprotected sectors must first be protected prior to the first sector unprotect write cycle. Note that the sector unprotect algorithm unprotects all sectors in par- ...

Page 22

Notes: 1. All protected sectors unprotected (If WP#/ACC = 2. All previously protected sectors are protected once Figure 1. Temporary Sector Unprotect Operation 22 START RESET (Note 1) Perform Erase or Program Operations RESET ...

Page 23

START PLSCNT = 1 RESET Wait First Write Temporary Sector Cycle = 60h? Unprotect Mode Yes Set up sector address Sector Protect: Write 60h to sector address with ...

Page 24

SecSi™ (Secured Silicon) Sector Flash Memory Region The SecSi (Secured Silicon) Sector feature provides a Flash memory region that enables permanent part identification through an Electronic Serial Number (ESN). The SecSi Sector is 256 bytes in length, and uses a ...

Page 25

The SecSi Sector area can be protected using one of the following procedures: Write the three-cycle Enter SecSi Sector Region command sequence, and then follow the in-system sector protect algorithm as shown in cept that RESET# may be at either ...

Page 26

Subsequent writes are ignored until V must provide the proper signals to the control pins to prevent unintentional writes when V is greater than V CC Write Pulse “Glitch” Protection Noise pulses of less than 5 ns (typical) on ...

Page 27

Addresses Addresses (Word Mode) (Byte Mode) 10h 20h 11h 22h 12h 24h 13h 26h 14h 28h 15h 2Ah 16h 2Ch 17h 2Eh 18h 30h 19h 32h 1Ah 34h Addresses Addresses (Word Mode) (Byte Mode) 1Bh 36h 1Ch 38h 1Dh 3Ah ...

Page 28

Addresses Addresses (Word Mode) (Byte Mode) 27h 4Eh 28h 50h 29h 52h 2Ah 54h 2Bh 56h 2Ch 58h 2Dh 5Ah 2Eh 5Ch 2Fh 5Eh 30h 60h 31h 62h 32h 64h 33h 66h 34h 68h 35h 6Ah 36h 6Ch 37h 6Eh ...

Page 29

Table 3. Primary Vendor-Specific Extended Query Addresses Addresses (Word Mode) (Byte Mode) 40h 80h 41h 82h 42h 84h 43h 86h 44h 88h 45h 8Ah 46h 8Ch 47h 8Eh 48h 90h 49h 92h 4Ah 94h 4Bh 96h 4Ch 98h 4Dh 9Ah ...

Page 30

Command Definitions Writing specific address and data commands or sequences into the command register initiates device operations. Table sequences. Writing incorrect address and data values or writing them in the im- proper sequence may place the device in an unknown ...

Page 31

If DQ5 goes high during a program or erase operation, writing the reset command returns the banks to the read mode (or erase-suspend-read mode if that bank was in Erase Suspend). Autoselect Command Sequence The autoselect command sequence allows the ...

Page 32

Any commands written to the device during the Embedded Program Algorithm are ignored. Note that a hardware reset immediately terminates the program operation. The program command sequence should be reinitiated once that bank has returned to the read mode, to ...

Page 33

Note: See Table Chip Erase Command Sequence Chip erase is a six bus cycle operation. The chip erase command sequence is ini- tiated by writing two unlock cycles, followed by a set-up command. Two additional unlock write cycles are then ...

Page 34

Refer to the Erase and Program Operations tables in the AC Characteristics section for parameters, and section for timing diagrams. Sector Erase Command Sequence Sector erase is a six bus cycle operation. ...

Page 35

Notes: 1. See Table 2. See the section on DQ3 for information on the sector Erase Suspend/Erase Resume Commands The Erase Suspend command, B0h, allows the system to interrupt a sector erase operation and then read data from, or program ...

Page 36

After an erase-suspended program operation is complete, the bank returns to the erase-suspend-read mode. The system can determine the status of the program operation using the DQ7 or DQ6 status bits, just as in the standard Byte Program operation. Refer ...

Page 37

Command Sequence (Note 1) Addr Read (Note 6) 1 Reset (Note 7) 1 Word Manufacturer ID 4 Byte Word Device ID (Note 9) 6 Byte Word SecSi Sector Factory 4 Protect (Note 10) Byte Sector/Sector Block Word Protect Verify 4 ...

Page 38

Write Operation Status The device provides several bits to determine the status of a program or erase operation: DQ2, DQ3, DQ5, DQ6, and DQ7. Table describe the function of these bits. DQ7 and DQ6 each offer a method for deter- ...

Page 39

April 28, 2004 S29JL064HA2 START Read DQ7–DQ0 Addr = VA Yes DQ7 = Data DQ5 = 1? Yes Read DQ7–DQ0 Addr = VA Yes DQ7 = Data? No FAIL Notes Valid address for programming. During ...

Page 40

RY/BY#: Ready/Busy# The RY/BY dedicated, open-drain output pin which indicates whether an Embedded Algorithm is in progress or complete. The RY/BY# status is valid after the rising edge of the final WE# pulse in the command sequence. Since ...

Page 41

Note: The system should recheck the toggle bit even if DQ5 = “1” because the toggle bit may stop toggling as DQ5 changes to “1.” See the subsections on DQ6 and DQ2 for more information. DQ2: Toggle Bit II The ...

Page 42

DQ2 toggles when the system reads at addresses within those sectors that have been selected for erasure. (The system may use either OE# or CE# to control the read cycles.) But DQ2 cannot distinguish whether the sector is actively erasing ...

Page 43

If additional sectors are selected for erasure, the entire time-out also applies after each additional sector erase command. When the time-out period is complete, DQ3 switches from a “0” “1.” If the ...

Page 44

Absolute Maximum Ratings Storage Temperature Plastic Packages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 45

DC Characteristics CMOS Compatible Paramete r Symbol Parameter Description I Input Load Current LI A9, OE# and RESET# Input Load I LIT Current I Output Leakage Current LO I Reset Leakage Current LR V Active Read Current CC I CC1 ...

Page 46

DC Characteristics Zero-Power Flash 500 1000 Note: Addresses are switching at 1 MHz Figure 10. I Current vs. Time (Showing Active and Automatic Sleep Currents) CC1 ...

Page 47

Test Conditions Note: Diodes are IN3064 or equivalent Test Condition Output Load Output Load Capacitance (including jig capacitance) Input Rise and Fall Times Input Pulse Levels Input timing measurement reference levels Output timing measurement reference levels Key To ...

Page 48

AC Characteristics Read-Only Operations Parameter JEDEC Std. Description t t Read Cycle Time (Note 1) AVAV Address to Output Delay AVQV ACC t t Chip Enable to Output Delay ELQV Output Enable to Output ...

Page 49

AC Characteristics Hardware Reset (RESET#) Parameter JEDEC Std RESET# Pin Low (During Embedded Algorithms) t Ready to Read Mode (See Note) RESET# Pin Low (NOT During Embedded t Ready Algorithms) to Read Mode (See Note) t RESET# Pulse Width RP ...

Page 50

AC Characteristics Word/Byte Configuration (BYTE#) Parameter JEDEC Std. Description t t CE# to BYTE# Switching Low or High ELFL/ ELFH t BYTE# Switching Low to Output HIGH Z FLQZ t BYTE# Switching High to Output Active FHQV 50 Speed Options ...

Page 51

CE# OE# BYTE# BYTE# DQ14–DQ0 Switching from word to byte mode DQ15/A-1 BYTE# BYTE# Switching DQ14–DQ0 from byte to word mode DQ15/A-1 Figure 16. BYTE# Timings for Read Operations CE# WE# BYTE# Note: Refer to the Erase/Program Operations table for ...

Page 52

AC Characteristics Erase and Program Operations Parameter JEDEC Std Description t t Write Cycle Time (Note 1) AVAV Address Setup Time AVWL AS Address Setup Time to OE# low during toggle bit t ASO polling t t ...

Page 53

AC Characteristics Program Command Sequence (last two cycles Addresses 555h CE# OE# WE Data RY/BY VCS Notes program address program data Illustration shows device in word ...

Page 54

AC Characteristics Erase Command Sequence (last two cycles Addresses 2AAh CE Data RY/BY# t VCS V CC Notes sector address (for Sector Erase Valid Address ...

Page 55

AC Characteristics t WC Valid PA Addresses t AH CE# OE WE# t WPH Valid Data In WE# Controlled Write Cycle Figure 21. Back-to-back Read/Write Cycle Timings t RC Addresses VA t ACC t CE ...

Page 56

AC Characteristics Addresses CE# t OEH WE# OE Valid Data DQ6/DQ2 RY/BY# Note Valid address; not required for DQ6. Illustration shows first two status cycle after command sequence, last status read cycle, and array data read ...

Page 57

AC Characteristics Temporary Sector Unprotect Parameter JEDEC Std Description t V Rise and Fall Time (See Note) VIDR Rise and Fall Time (See Note) VHH HH RESET# Setup Time for Temporary Sector t RSP Unprotect RESET# Hold ...

Page 58

AC Characteristics RESET# SA, A6, A1, A0 Sector Group Protect/Unprotect Data 60h 1 µs CE# WE# OE# * For sector protect For sector unprotect ...

Page 59

AC Characteristics Alternate CE# Controlled Erase and Program Operations Parameter JEDEC Std. Description t t Write Cycle Time (Note 1) AVAV Address Setup Time AVWL Address Hold Time ELAX Data Setup ...

Page 60

AC Characteristics 555 for program 2AA for erase Addresses WE# OE# CE Data t RH RESET# RY/BY# Notes: 1. Figure indicates last two bus cycles of a program or erase operation ...

Page 61

Erase And Programming Performance Parameter Sector Erase Time Chip Erase Time Byte Program Time Accelerated Byte/Word Program Time Accelerated Chip Programming Time Word Program Time Byte Mode Chip Program Time (Note 3) Word Mode Notes: 1. Typical program and erase ...

Page 62

Physical Dimensions FBE063—63-Ball Fine-Pitch Ball Grid Array (BGA package 62 S29JL064H Dwg rev AF; 10/99 S29JL064HA2 April 28, 2004 ...

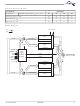

Page 63

Physical Dimensions TS 048—48-Pin Standard TSOP April 28, 2004 S29JL064HA2 Dwg rev AA; 10/99 S29JL064H 63 ...

Page 64

Revision Summary Revision A (January 22, 2004) Initial release. Revision (March 26, 2004) Removed “Latchup Characteristics” section. Revision (April 28, 2004) Updated datasheet status from “Preliminary” to “Datasheet”. Trademarks and Notice The contents of ...