AM186EM-40KC/W Advanced Micro Devices, AM186EM-40KC/W Datasheet

AM186EM-40KC/W

Related parts for AM186EM-40KC/W

AM186EM-40KC/W Summary of contents

Page 1

... The Am186EM/EMLV and Am188EM/EMLV microcon- trollers have been designed to meet the most common requirements of embedded products developed for the office automation, mass storage, communications, and general embedded markets ...

Page 2

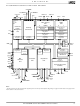

... Am186EM MICROCONTROLLER BLOCK DIAGRAM INT2/INTA0 INT3/INTA1/IRQ CLKOUTA INT4 CLKOUTB X2 X1 Clock and Power Control Unit Management V CC Unit GND Control Registers RES Control Refresh Registers Control ARDY Unit SRDY S2–S0 DT/R Bus DEN Interface HOLD Unit HLDA S6/ CLKDIV2 UZI WHB A19–A0 WLB AD15– ...

Page 3

Am188EM MICROCONTROLLER BLOCK DIAGRAM INT2/INTA0 INT3/INTA1/IRQ CLKOUTA INT4 CLKOUTB X2 X1 Clock and Interrupt Power Control Unit Management V CC Unit GND Control Control Registers Registers RES Control Refresh Registers Control ARDY Unit SRDY S2–S0 DT/R Bus DEN Interface Unit ...

Page 4

... Notes: VC The Am186EM and Am188EM industrial KC\W microcontrollers, as well as the Am186EMLV and Am188EMLV commercial microcontrollers, are available in 20- and 25-MHz operating frequencies only. KI\W 2. The Am186EM and Am188EM industrial microcontrollers are not offered in a low-voltage KI\W operating range ...

Page 5

... TABLE OF CONTENTS Distinctive Characteristics ............................................................................................................ 1 General Description ..................................................................................................................... 1 Am186EM Microcontroller Block Diagram .................................................................................... 2 Am188EM Microcontroller Block Diagram .................................................................................... 3 Ordering Information .................................................................................................................... 4 Related AMD Products ................................................................................................................ 8 Key Features and Benefits ........................................................................................................ 10 TQFP Connection Diagrams and Pinouts .................................................................................. 11 PQFP Connection Diagrams and Pinouts ................................................................................. 17 Logic Symbol—Am186EM Microcontroller ................................................................................ 23 Logic Symbol—Am188EM Microcontroller ................................................................................ 24 Pin Descriptions Pins that Are Used by Emulators ...

Page 6

... TMRIN1/PIO0 ................................................................................................................ 32 TMROUT0/PIO10 .......................................................................................................... 32 TMROUT1/PIO1 ............................................................................................................ 32 TXD/PIO27 ..................................................................................................................... 32 UCS/ONCE1 .................................................................................................................. 32 UZI/PIO26 ...................................................................................................................... 33 V ................................................................................................................................. 33 CC WHB (Am186EM Microcontroller Only) ......................................................................... 33 WLB (Am186EM Microcontroller Only) ........................................................................... 33 WB (Am188EM Microcontroller Only) ............................................................................ 33 WR ................................................................................................................................. 33 X1 ................................................................................................................................... 33 X2 ................................................................................................................................... 33 Functional Description ............................................................................................................... 34 Bus Operation ............................................................................................................................ 35 Bus Interface Unit ....................................................................................................................... 37 Peripheral Control Block (PCB) ................................................................................................. 38 Clock and Power Management .................................................................................................. 41 Chip-Select Unit.......................................................................................................................... 43 Refresh Control Unit .................................................................................................................. 45 Interrupt Control Unit ...

Page 7

... LIST OF FIGURES Figure 1. Example System Design ........................................................................................ 10 Figure 2. Two-Component Address ...................................................................................... 34 Figure 3. Am186EM Microcontroller Address Bus—Normal Read and Write Operation ...... 35 Figure 4. Am186EM Microcontroller—Read and Write with Address Bus Disable In Effect ..................................................................................................... 36 Figure 5. Am188EM Microcontroller Address Bus—Normal Read and Write Operation ...... 36 Figure 6. ...

Page 8

... Am186EM High-performance, 80C186-compatible, 16-bit embedded microcontroller Am188EM High-performance, 80C188-compatible, 16-bit embedded microcontroller with 8-bit external data bus Am186EMLV High-performance, 80C186-compatible, low-voltage, 16-bit embedded microcontroller Am188EMLV High-performance, 80C188-compatible, low-voltage, 16-bit embedded microcontroller with 8-bit external data bus Am186ES High-performance, 80C186-compatible, 16-bit embedded microcontroller ...

Page 9

... Related Documents The following documents provide additional informa- tion regarding the Am186EM and Am188EM microcon- trollers. The Am186EM and Am188EM Microcontrollers User’s Manual, order# 19713 The Am186 and Am188 Family Instruction Set Manual, order# 21267 SM The FusionE86 Catalog, order# 19255 ...

Page 10

... Upgr adi ng to the Am 186EM and Am188EM microcontrollers is an attractive solution for several reasons: Minimized total system cost—New peripherals and on-chip system interface logic on the Am186EM and Am188EM microcontrollers reduce the cost of existing 80C186/188 designs. X86 software compatibility—80C186/188-com- patible and upward-compatible with the other mem- bers of the AMD E86 family ...

Page 11

... CC AD14 16 AD7 17 AD15 18 19 S6/CLKDIV2 20 UZI TXD 21 RXD 22 SDATA 23 SDEN1 24 SDEN0 25 Note : Pin 1 is marked for orientation. Am186/188EM and Am186/188EMLV Microcontrollers Am186EM Microcontroller 75 INT4 74 MCS1 73 MCS0 72 DEN 71 DT/R 70 NMI 69 SRDY 68 HOLD 67 HLDA 66 WLB 65 WHB 64 GND 63 ...

Page 12

... TQFP PIN ASSIGNMENTS—Am186EM Microcontroller (Sorted by Pin Number) Pin No. Name Pin No. Name 1 AD0 26 2 AD8 27 3 AD1 28 4 AD9 29 5 AD2 30 6 AD10 31 7 AD3 32 8 AD11 33 9 AD4 34 10 AD12 35 11 AD5 36 12 GND 37 13 AD13 38 14 AD6 ...

Page 13

... TQFP PIN ASSIGNMENTS—Am186EM Microcontroller (Sorted by Pin Name) Pin Name No. Pin Name A0 63 AD5 A1 62 AD6 A2 60 AD7 A3 59 AD8 A4 58 AD9 A5 57 AD10 A6 56 AD11 A7 55 AD12 A8 54 AD13 A9 53 AD14 A10 52 AD15 A11 51 ALE A12 50 ARDY A13 49 BHE/ADEN A14 ...

Page 14

CONNECTION DIAGRAM Am188EM Microcontroller Top Side View—100-Pin Thin Quad Flat Pack (TQFP) AD0 1 AO8 2 AD1 3 AO9 4 AD2 5 AO10 6 AD3 7 AO11 8 AD4 9 AO12 10 AD5 11 GND 12 AO13 13 AD6 14 ...

Page 15

TQFP PIN ASSIGNMENTS—Am188EM Microcontroller (Sorted by Pin Number) Pin No. Name Pin No. Name 1 AD0 26 2 AO8 27 3 AD1 28 4 AO9 29 5 AD2 30 6 AO10 31 7 AD3 32 8 AO11 33 9 AD4 ...

Page 16

TQFP PIN ASSIGNMENTS—Am188EM Microcontroller (Sorted by Pin Name) Pin Name No. Pin Name A0 63 AD5 A1 62 AD6 A2 60 AD7 A3 59 ALE A4 58 AO8 A5 57 AO9 A6 56 AO10 A7 55 AO11 A8 54 AO12 ...

Page 17

... A18 A17 23 A16 24 A15 25 A14 26 A13 27 A12 28 A11 29 A10 30 A9 Note: Pin 1 is marked for orientation. Am186/188EM and Am186/188EMLV Microcontrollers Am186EM Microcontroller 80 AD1 79 AD8 78 AD0 77 DRQ0 76 DRQ1 75 TMRIN0 74 TMROUT0 73 TMROUT1 72 TMRIN1 71 RES 70 GND 69 MCS3/RFSH 68 ...

Page 18

... PQFP PIN ASSIGNMENTS—Am186EM Microcontroller (Sorted by Pin Number) Pin No. Name Pin No. Name 1 SDEN1/PIO23 26 2 SDEN0/PIO22 27 3 SCLK/PIO20 28 4 BHE/ADEN ALE 32 8 ARDY GND CLKOUTA 41 17 CLKOUTB ...

Page 19

... PQFP PIN ASSIGNMENTS—Am186EM Microcontroller (Sorted by Pin Name) Pin Name No. Pin Name A0 40 AD5 A1 39 AD6 A2 37 AD7 A3 36 AD8 A4 35 AD9 A5 34 AD10 A6 33 AD11 A7 32 AD12 A8 31 AD13 A9 30 AD14 A10 29 AD15 A11 28 ALE A12 27 ARDY A13 26 BHE/ADEN A14 ...

Page 20

CONNECTION DIAGRAM Am188EM Microcontroller Top Side View—100-Pin Plastic Quad Flat Pack (PQFP) 1 SDEN1 2 SDEN0 3 SCLK 4 RFSH2/ADEN ALE 7 8 ARDY GND ...

Page 21

PQFP PIN ASSIGNMENTS—Am188EM Microcontroller (Sorted by Pin Number) Pin No. Name Pin No. Name 1 SDEN1/PIO23 26 2 SDEN0/PIO22 27 3 SCLK/PIO20 28 4 RFSH2/ADEN ALE 32 8 ARDY ...

Page 22

PQFP PIN ASSIGNMENTS—Am188EM Microcontroller (Sorted by Pin Name) Pin Name No. Pin Name A0 40 AD5 A1 39 AD6 A2 37 AD7 A3 36 ALE A4 35 AO8 A5 34 AO9 A6 33 AO10 A7 32 AO11 A8 31 AO12 ...

Page 23

... LOGIC SYMBOL—Am186EM MICROCONTROLLER Clocks 20 * Address and 16 Address/Data Buses * * 3 Bus Control * * * * * Timer Control * * 32 shared Programmable ** I/O Control Notes: * These signals are the normal function of a pin that can be used as a PIO. See the pin descriptions beginning on page 25 and Table 2 on page 30 for information on shared function. ...

Page 24

LOGIC SYMBOL—Am188EM MICROCONTROLLER Clocks * 20 8 Address and Address/Data Buses Bus Control * * * * * Timer Control * * 32 shared Programmable ** I/O Control Notes: * These signals are the normal function ...

Page 25

... Pins That Are Used by Emulators The following pins are used by emulators: A19–A0, AO15–AO8, AD7–AD0, ALE, BHE/ADEN (on the Am186EM), CLKOUTA 2 (on the Am188EM), RD, S2–S0, S6/CLKDIV2, and UZI. Emulators require that S6/CLKDIV2 and UZI be config- ured in their normal functionality, that and UZI. ...

Page 26

... BHE does not need to be latched BHE floats during bus hold and reset. On the Am186EM and Am188EM microcontrollers, WLB and WHB implement the functionality of BHE and AD0 for high and low byte write enables. Table 1. Data Byte Encoding BHE ...

Page 27

... This pin indicates to the microcontroller that an external bus master needs control of the local bus. The Am186EM and Am188EM microcontrollers’ HOLD latency time is a function of the activity occurring in the processor when the HOLD request is received. A DRAM request will delay a HOLD request when both requests are made at the same time ...

Page 28

Interrupt requests are synchronized internally, and can be edge-triggered or level-triggered. To guarantee in- terrupt recognition, the requesting device must con- tinue asserting INT3 until the request is acknowledged. INT3 becomes INTA1 when INT1 is configured in cas- cade mode. ...

Page 29

... PCS3–PCS0 are held High during a bus hold condition. They are also held High during reset. PCS4 is not available on the Am186EM and Am188EM microcontrollers. Unlike the UCS and LCS chip selects, the PCS outputs assert with the multiplexed AD address bus. Note also ...

Page 30

Table 2. Numeric PIO Pin Assignments PIO No Associated Pin Power-On Reset Status 0 TMRIN1 Input with pullup 1 TMROUT1 Input with pulldown 2 PCS6/A2 Input with pullup 3 PCS5/A1 Input with pullup 4 DT/R Normal operation 5 DEN Normal ...

Page 31

RD Read Strobe (output, synchronous, three-state) This pin indicates to the system that the microcontroller is performing a memory or I/O read cycle guar- anteed not to be asserted before the address and data bus is floated during ...

Page 32

SCLK/PIO20 Serial Clock (output, synchronous) This pin supplies the synchronous serial interface (SSI) clock to a slave device, allowing transmit and receive operations to be synchronized between the microcon- troller and the slave. SCLK is derived from the micro- controller ...

Page 33

... This signal should be pulled High or allowed to float at reset. If this pin is Low at the negation of reset, the Am186EM and Am188EM microcontrollers will enter a re- served clock test mode Power Supply (input) These pins supply power (+ the microcontroller ...

Page 34

... All family members contain the same basic set of registers, instructions, and addressing modes and are compatible with the industry-standard 80C186/188 microcontrollers. A full description of all the Am186EM and Am188EM microcontroller registers is included in the Am186EM and Am188EM Microcontrollers User’s Manual , order# 19713. The instruction set for the Am186EM and Am188EM microcontrollers is documented in the Am186 and Am188 Family Instruction Set Manual , order# 21267 ...

Page 35

... For systems where power consumption is a concern possible to disable the address from being driven on the AD bus on the Am186EM microcontroller and on the AD and AO buses on the Am188EM microcontroller during the normal address portion of the bus cycle for accesses to UCS and/or LCS address spaces. In this mode, the affected bus is placed in a high impedance state during the address portion of the bus cycle ...

Page 36

... CLKOUTA A19–A0 AD7–AD0 (Read) AD15–AD8 (Read) AD15–AD0 (Write) LCS, UCS Figure 4. Am186EM Microcontroller—Read and Write with Address Bus Disable In Effect CLKOUTA A19–A0 AD7–AD0 (Read) AO15–AO8 (Read or Write) AD7–AD0 (Write) LCS or UCS MCSx, PCSx Figure 5. Am188EM Microcontroller Address Bus— ...

Page 37

... Pseudo Static RAM (PSRAM) support The standard 80C186/188 multiplexed address and data bus requires system interface logic and an exter- nal address latch. On the Am186EM and Am188EM microcontrollers, new byte write enables, PSRAM con- trol logic, and a new nonmultiplexed address bus can reduce design costs by eliminating this external logic ...

Page 38

... When PSRAM mode is enabled, the timing for the LCS signal is modified by the chip-select control unit to provide a CS precharge period during PSRAM accesses. The 40-MHz timing of the Am186EM and Am188EM microcontrollers is appropriate to allow 70-ns PSRAM to run with one wait state. PSRAM mode is enabled through a bit in the Low Memory Chip-Select (LMCS) Register ...

Page 39

Offset (Hexadecimal) Register Name FE Peripheral Control Block Relocation Register Reset Configuration Register F6 Processor Release Level Register F4 F0 PDCON Register E4 Enable RCU Register E2 Clock Prescaler ...

Page 40

Offset (Hexadecimal Timer 2 Maxcount Compare A Register 60 5E Timer 1 Maxcount Compare B Register 5C Timer 1 Maxcount Compare A Register Timer 0 Maxcount Compare B Register ...

Page 41

... This removes the need for an external 2x oscillator, reducing system cost. The PLL is reset by an on-chip power-on reset (POR) circuit. Crystal-Driven Clock Source The internal oscillator circuit of the Am186EM and Am188EM microcontrollers is designed to function with a parallel-resonant fundamental or third-overtone crys- tal. Because of the PLL, the crystal frequency should be equal to the processor frequency ...

Page 42

... RES input pin Low. RES must be held Low for 1 ms during power-up to ensure proper device initializa- tion. RES forces the Am186EM and Am188EM microcon- trollers to terminate all execution and local bus activity. No instruction or bus activity occurs as long as RES is active. ...

Page 43

... Chip-Select Overlap Although programming the various chip selects on the Am186EM and Am188EM microcontrollers so that mul- tiple chip select signals are asserted for the same physical address is not recommended, it may be un- avoidable in some systems. In such systems, the chip ...

Page 44

... The Am186EM and Am188EM microcontrollers pro- vide six chip selects, PCS6–PCS5 and PCS3–PCS0, for use within a user-locatable memory or I/O block. PCS4 is not available on the Am186EM and Am188EM microcontrollers. The base address of the memory block can be located anywhere within the 1-Mbyte ...

Page 45

... Am186/188EM and Am186/188EMLV Microcontrollers INTERRUPT CONTROL UNIT The Am186EM and Am188EM microcontrollers can re- ceive interrupt requests from a variety of sources, both internal and external. The internal interrupt controller arranges these requests by priority and presents them one at a time to the CPU ...

Page 46

... I/O spaces (e.g., memory to I/O) or within the same space (e.g., memory-to-memory or I/O-to- I/O). In addition, either bytes or words can be transferred to or from even or odd addresses on the Am186EM micro- controller. The Am188EM microcontroller does not sup- port word transfers. Only two bus cycles (a minimum of eight clocks) are necessary for each data transfer ...

Page 47

Adder/Subtractor 20 Transfer Counter Ch. 1 Destination Address Ch. 1 Source Address Ch. 1 Transfer Counter Ch. 0 Destination Address Ch. 0 Source Address Ch DMA Channel Control Registers Each DMA control register determines the mode of ...

Page 48

... The two enable pins SDEN1–SDEN0 can be used di- rectly as enables for up to two peripheral devices. Transmit and receive operations are synchronized be- tween the master (Am186EM and Am188EM micro- controllers) and slave (peripheral) by means of the SCLK output. SCLK is derived from the internal proces- sor clock and is the processor clock divided ...

Page 49

PB=0 PB=1 PB=0 DR/DT=0 DR/DT=0 DR/DT=1 SDEN SCLK SDATA Poll SSS for PB=0 Write to SSD Write to SSC, bit DE=1 Figure 11. PB=0 PB=1 PB=0 DR/DT=1 DR/DT=0 DR/DT=0 SDEN SCLK SDATA Poll SSS for PB=0 Write to SSD Write ...

Page 50

... PROGRAMMABLE I/O (PIO) PINS There are 32 pins on the Am186EM and Am188EM mi- crocontrollers that are available as user multipurpose signals. Table 2 and Table 3 on page 30 list the PIO pins. Each of these pins can be used as a user-pro- grammable input or output signal if the normal shared function is not needed. ...

Page 51

... Current is measured with the device in RESET with X1 and X2 driven, and all other non-power pins open but held High or Low. c Power supply current for the Am186EMLV and Am188EMLV microcontrollers, which are available in 20 and 25 MHz operating frequencies only. d Testing is performed with the pins floating, either during HOLD or by invoking the ONCE mode. ...

Page 52

... Am186EMLV and Am188EMLV Measured Peak Measured with a device running. Not tested and not guaranteed. b Power supply current for the Am186EMLV and Am188EMLV microcontrollers, which are available in 20 and 25 MHz operating frequencies only. c Power is measured while device is operating. Not tested and not guaranteed. ...

Page 53

... I (mA Figure 13. Typical I Am186EMLV and Am188EMLV 33 MHz 25 MHz 20 MHz Clock Frequency (MHz) Versus Frequency for the Am186EM and Am188EM CC Volts / 1000 = P Typical Power in Watts Typical I Volts CC 3.0 3.6 0.173 3.0 3.6 0.216 3.0 3.6 0.270 25 MHz 20 MHz 16 MHz 10 20 ...

Page 54

... Am186EM and Am188EM ...

Page 55

... Typical Ambient Temperatures The typical ambient temperature specifications are based on the following assumptions and calculations: The commercial operating range of the Am186EM and Am188EM microcontrollers is a case temperature 100 degrees Centigrade measured at the top C center of the package. An increase in the ambient tem- perature causes a proportional increase in T The 40-MHz microcontroller is specified as 5 ...

Page 56

Table 11 shows typical maximum ambient temperatures in degrees Centigrade for a PQFP package used with a 2-layer board. The typical ambient temperatures are based on a 100-degree Centigrade maximum case tempera- ture. Figure 17 illustrates the typical temperatures in ...

Page 57

Table 12 shows typical maximum ambient temperatures in degrees Centigrade for a TQFP package used with a 2-layer board. The typical ambient temperatures are based on a 100-degree Centigrade maximum case tempera- ture. Figure 18 illustrates the typical temperatures in ...

Page 58

Table 13 shows typical maximum ambient temperatures in degrees Centigrade for a PQFP package used with a 4-layer to 6-layer board. The typical ambient temperatures are based on a 100-degree Centigrade maximum case temperature. Figure 19 illustrates the typical temperatures ...

Page 59

Table 14 shows typical maximum ambient temperatures in degrees Centigrade for a TQFP package used with a 4-layer to 6-layer board. The typical ambient temperatures are based on a 100-degree Centigrade maximum case temperature. Figure 20 illustrates the typical temperatures ...

Page 60

COMMERCIAL SWITCHING CHARACTERISTICS AND WAVEFORMS In the switching waveforms that follow, several abbre- viations are used to indicate the specific periods of a bus cycle. These periods are referred to as time states. A typical bus cycle is composed of ...

Page 61

Alphabetical Key to Switching Parameter Symbols Parameter Symbol No. Description t 49 ARDY Resolution Transition Setup Time ARYCH t 51 ARDY Inactive Holding Time ARYCHL t 52 ARDY Setup Time ARYLCL Address Valid to WHB, WLB Low ...

Page 62

Numerical Key to Switching Parameter Symbols Parameter Number Symbol Description 1 t Data in Setup DVCL 2 t Data in Hold CLDX 3 t Status Active Delay CHSV 4 t Status Inactive Delay CLSH Address Valid Delay ...

Page 63

SWITCHING CHARACTERISTICS over COMMERCIAL operating range Read Cycle (20 MHz and 25 MHz) Parameter No. Symbol Description General Timing Requirements 1 t Data in Setup DVCL ( Data in Hold CLDX General Timing Responses 3 t Status Active ...

Page 64

SWITCHING CHARACTERISTICS over COMMERCIAL operating range Read Cycle (33 MHz and 40 MHz) Parameter No. Symbol Description General Timing Requirements 1 t Data in Setup DVCL ( Data in Hold CLDX General Timing Responses 3 t Status Active ...

Page 65

... MCS1–MCS0, PCS6–PCS5, PCS3–PCS0 DEN 19 DT/R *** 22 S2–S0 3 UZI Notes: * Am186EM microcontroller only ** Am188EM microcontroller only *** Changes in t phase of the clock preceding next bus cycle if followed by read, INTA, or halt 4 Am186/188EM and Am186/188EMLV Microcontrollers ...

Page 66

SWITCHING CHARACTERISTICS over COMMERCIAL operating range Write Cycle (20 MHz and 25 MHz) Parameter No. Symbol Description General Timing Responses 3 t Status Active Delay CHSV 4 t Status Inactive Delay CLSH Address Valid Delay and BHE ...

Page 67

SWITCHING CHARACTERISTICS over COMMERCIAL operating range Write Cycle (33 MHz and 40 MHz) Parameter No. Symbol Description General Timing Responses 3 t Status Active Delay CHSV 4 t Status Inactive Delay CLSH Address Valid Delay and BHE ...

Page 68

... MCS3–MCS0, PCS6–PCS5, PCS3–PCS0 DEN DT/R *** 22 S2–S0 3 UZI Note: * Am186EM microcontroller only ** Am188EM microcontroller only *** Changes in t phase of the clock preceding next bus cycle if followed by read, INTA, or halt Am186/188EM and Am186/188EMLV Microcontrollers ...

Page 69

SWITCHING CHARACTERISTICS over COMMERCIAL operating range PSRAM Read Cycle (20 MHz and 25 MHz) Parameter No. Symbol Description General Timing Requirements 1 t Data in Setup DVCL ( Data in Hold CLDX General Timing Responses ...

Page 70

SWITCHING CHARACTERISTICS over Commercial operating range PSRAM Read Cycle (33 MHz and 40 MHz) Parameter No. Symbol Description General Timing Requirements 1 t Data in Setup DVCL ( Data in Hold CLDX General Timing Responses ...

Page 71

... PSRAM Read Cycle Waveforms CLKOUTA A19– AD15–AD0*, AD7–AD0** AO15–AO8 ALE RD 27 LCS 80 84 Notes: * Am186EM microcontroller only ** Am188EM microcontroller only Am186/188EM and Am186/188EMLV Microcontrollers Address 7 Address Address ...

Page 72

SWITCHING CHARACTERISTICS over COMMERCIAL operating range PSRAM Write Cycle (20 MHz and 25 MHz) Parameter No. Symbol Description General Timing Responses AD Address Valid Delay and 5 t CLAV BHE 7 t Data Valid Delay CLDV 8 t Status Hold ...

Page 73

SWITCHING CHARACTERISTICS over COMMERCIAL operating range PSRAM Write Cycle (33 MHz and 40 MHz) Parameter No. Symbol Description General Timing Responses AD Address Valid Delay and 5 t CLAV BHE 7 t Data Valid Delay CLDV 8 t Status Hold ...

Page 74

... A19– AD15–AD0*, AD7–AD0** AO15–AO8 ALE WHB*, WLB* 87 WB** LCS 80 84 Notes: * Am186EM microcontroller only ** Am188EM microcontroller only 74 Am186/188EM and Am186/188EMLV Microcontrollers Address 7 Address Address ...

Page 75

SWITCHING CHARACTERISTICS over COMMERCIAL operating range PSRAM Refresh Cycle (20 MHz and 25 MHz) Parameter No. Symbol Description General Timing Responses 9 t ALE Active Delay CHLH 10 t ALE Width LHLL 11 t ALE Inactive Delay CHLL Read/Write Cycle ...

Page 76

SWITCHING CHARACTERISTICS over COMMERCIAL operating range PSRAM Refresh Cycle (33 MHz and 40 MHz) Parameter No. Symbol Description General Timing Responses 9 t ALE Active Delay CHLH 10 t ALE Width LHLL 11 t ALE Inactive Delay CHLL Read/Write Cycle ...

Page 77

PSRAM Refresh Cycle Waveforms CLKOUTA A19–A0 9 ALE LCS RFSH 86 Note: * The period tw is fixed at 3 wait states for PSRAM auto refresh only. Am186/188EM and Am186/188EMLV Microcontrollers ...

Page 78

SWITCHING CHARACTERISTICS over COMMERCIAL operating range Interrupt Acknowledge Cycle (20 MHz and 25 MHz) Parameter No. Symbol Description General Timing Requirements 1 t Data in Setup DVCL 2 t Data in Hold CLDX General Timing Responses 3 t Status Active ...

Page 79

SWITCHING CHARACTERISTICS over COMMERCIAL operating range Interrupt Acknowledge Cycle (33 MHz and 40 MHz) Parameter No. Symbol Description General Timing Requirements 1 t Data in Setup DVCL 2 t Data in Hold CLDX General Timing Responses 3 t Status Active ...

Page 80

... DEN 22 DT/R S2–S0 Notes: * Am186EM microcontroller only ** Am188EM microcontroller only a The status bits become inactive in the state preceding t b The data hold time lasts only until the interrupt acknowledge signal deasserts, even if the interrupt acknowledge transition occurs prior to t CLDX c This parameter applies for an interrupt acknowledge cycle that follows a write cycle. ...

Page 81

SWITCHING CHARACTERISTICS over COMMERCIAL operating range Software Halt Cycle (20 MHz and 25 MHz) Parameter No. Symbol Description General Timing Responses 3 t Status Active Delay CHSV 4 t Status Inactive Delay CLSH AD Address Invalid Delay and 5 t ...

Page 82

SWITCHING CHARACTERISTICS over COMMERCIAL operating range Software Halt Cycle (33 MHz and 40 MHz) Parameter No. Symbol Description General Timing Responses 3 t Status Active Delay CHSV 4 t Status Inactive Delay CLSH AD Address Invalid Delay and 5 t ...

Page 83

... Software Halt Cycle Waveforms CLKOUTA 68 A19–A0 5 S6, AD15–AD0*, AD7–AD0**, AO15-AO8** ALE 9 DEN 19 DT/R S2–S0 3 Notes: * Am186EM microcontroller only ** Am188EM microcontroller only Am186/188EM and Am186/188EMLV Microcontrollers Invalid Address Invalid Address Status t ...

Page 84

SWITCHING CHARACTERISTICS over COMMERCIAL operating range Clock (20 MHZ and 25 MHz) Parameter No. Symbol Description CLKIN Requirements ( Period CKIN Low Time (1.5 V) CLCK High Time (1.5 V) CHCK ...

Page 85

SWITCHING CHARACTERISTICS over COMMERCIAL operating range Clock (33 MHZ and 40 MHz) Parameter No. Symbol Description CLKIN Requirements ( Period CKIN Low Time (1.5 V) CLCK High Time (1.5 V) CHCK ...

Page 86

Clock Waveforms—Active Mode CLKOUTA (Active, F=000) CLKOUTB Clock Waveforms—Power-Save Mode X2 X1 (a) CLKOUTA (b) CLKOUTB (c) CLKOUTB Notes: a The Clock Divisor Select (F2–F0) bits in the Power Save Control Register (PDCON) are set to 010 ...

Page 87

SWITCHING CHARACTERISTICS over COMMERCIAL operating range Ready and Peripheral Timing (20 MHz and 25 MHz) Parameter No. Symbol Description Ready and Peripheral Timing Requirements 47 t SRDY Transition Setup Time SRYCL 48 t SRDY Transition Hold Time CLSRY ARDY Resolution ...

Page 88

SWITCHING CHARACTERISTICS over COMMERCIAL operating range Ready and Peripheral Timing (33 MHz and 40 MHz) Parameter No. Symbol Description Ready and Peripheral Timing Requirements 47 t SRDY Transition Setup Time SRYCL 48 t SRDY Transition Hold Time CLSRY ARDY Resolution ...

Page 89

Asynchronous Ready Waveforms Case 1 Case 2 Case 3 Case 4 CLKOUTA ARDY (Normally Not- Ready System) ARDY (Normally Ready System) Peripheral Waveforms CLKOUTA INT4–INT0, NMI, TMRIN1–TMRIN0 DRQ1–DRQ0 TMROUT1– TMROUT0 Am186/188EM and Am186/188EMLV Microcontrollers ...

Page 90

SWITCHING CHARACTERISTICS over COMMERCIAL operating range Reset and Bus Hold (20 MHz and 25 MHz) Parameter No. Symbol Description Reset and Bus Hold Timing Requirements Address Valid Delay and BHE CLAV Address Float Delay ...

Page 91

Reset Waveforms X1 RES CLKOUTA Signals Related to Reset Waveforms RES CLKOUTA BHE/ADEN, RFSH2/ADEN, S6/CLKDIV2, and UZI AD15–AD0 (186) AO15–AO8, AD7–AD0 (188) Am186/188EM and Am186/188EMLV Microcontrollers three-state 57 ...

Page 92

Bus Hold Waveforms—Entering CLKOUTA 58 HOLD HLDA AD15–AD0, DEN A19–A0, S6, RD, WR, BHE, DT/R, S2–S0 WHB, WLB Bus Hold Waveforms—Leaving Case 1 Case 2 CLKOUTA HOLD HLDA AD15–AD0, DEN A19–A0, S6, RD, WR, BHE, DT/R, S2–S0 WHB, WLB 92 ...

Page 93

SWITCHING CHARACTERISTICS over COMMERCIAL operating range Synchronous Serial Interface (SSI) (20 MHz and 25 MHz) Parameter No. Symbol Description Synchronous Serial Port Timing Requirements 75 t Data Valid to SCLK High DVSH 77 t SCLK High to SPI Data Hold ...

Page 94

Synchronous Serial Interface (SSI) Waveforms CLKOUTA SDEN SCLK SDATA (RX) SDATA (TX) Note: SDATA is bidirectional and used for either transmit (TX) or receive (RX). Timing is shown separately for each case. 94 Am186/188EM and Am186/188EMLV Microcontrollers ...

Page 95

TQFP PHYSICAL DIMENSIONS PQL 100, Trimmed and Formed Thin Quad Flat Pack Pin 100 Pin 1 ID 12.00 – – A Ref Pin 25 See Detail X 1.35 1.45 1.00 Ref Notes: 1. All measurements are in millimeters unless otherwise ...

Page 96

PQL 100 (continued) 0 Min 0.13 R 1.60 0.20 Max Gage 0.25 Plane 0.45 0.75 0.20 Notes: 1. All measurements are in millimeters unless otherwise noted. 2. Not to scale; for reference only. 96 Am186/188EM and Am186/188EMLV Microcontrollers P R ...

Page 97

PQFP PHYSICAL DIMENSIONS PQR 100, Trimmed and Formed Plastic Quad Flat Pack Pin 100 Pin 1 I.D. – – Pin 30 See Detail X 2.70 2.90 0.25 Min Notes: 1. All measurements are in millimeters unless otherwise noted. ...

Page 98

... AMD, the AMD logo, and combinations thereof are trademarks of Advanced Micro Devices, Inc. Am386 and Am486 are registered trademarks of Advanced Micro Devices, Inc. Am186, Am188, E86, K86, Élan, and AMD Facts-On-Demand are trademarks of Advanced Micro Devices, Inc. FusionE86 is a service mark of Advanced Micro Devices, Inc. ...