M2V56S40TP-6 MITSUBISHI, M2V56S40TP-6 Datasheet

M2V56S40TP-6

Related parts for M2V56S40TP-6

M2V56S40TP-6 Summary of contents

Page 1

... M2V56S20TP is a 4-bank x 16777216-word x 4-bit, M2V56S30TP is a 4-bank x 8388608-word x 8-bit, M2V56S40TP is a 4-bank x 4194304-word x 16-bit, synchronous DRAM, with LVTTL interface. All inputs and outputs are referenced to the rising edge of CLK. The M2V56S20/30/40TP achieve very high speed data rate up to 100MHz (-7/-8) , 133MHz (-6), and are suitable for main memory or graphic memory in computer systems ...

Page 2

... Chip Select : Row Address Strobe : Column Address Strobe : Write Enable : Data I/O : Address Input : Bank Address Input : Power Supply : Power Supply for Output : Ground : Ground for Output MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM 54 Vss Vss Vss 53 DQ15 DQ7 NC 52 VssQ VssQ ...

Page 3

... Process Generation Function Reserved for Future Use Organization x4, 3: x8, 4: x16 SDRAM Data Rate Type S:Single Data Rate Density 56: 256M bits Interface V:LVTTL Memory Style (DRAM) Mitsubishi Main Designation MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM Memory Array Bank #3 Control Signal Buffer ...

Page 4

... When DQMU/L is high in burst read, Dout is disabled at the next but one cycle. Power Supply for the memory array and peripheral circuitry. VddQ and VssQ are supplied to the Output Buffers only. MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM 4 ...

Page 5

... REFA command starts auto-refresh cycle. Refresh address are generated internally. After this command, the banks are precharged automatically. M2V56S20/ 30/ 40/ TP -6, -7, -8 Chip Select : L=select, H=deselect Command Command define basic commands Command Refresh Option @refresh command Precharge Option @precharge or read/write command MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM 5 ...

Page 6

... MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM A10 /RAS /CAS /WE BA0,1 / ...

Page 7

... BA, CA, A10 L L BA, CA, A10 BA, A10 Op-Code Mode-Add MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM Command Action DESEL NOP NOP NOP TBST ILLEGAL*2 READ / WRITE ILLEGAL*2 ACT Bank Active, Latch RA PRE / PREA NOP*4 REFA Auto-Refresh*5 MRS ...

Page 8

... H BA BA, A10 Op-Code Mode-Add MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM Command Action DESEL NOP (Continue Burst to END) NOP NOP (Continue Burst to END) TBST Terminate Burst Terminate Burst, Latch CA, Begin Read, Determine Auto- Precharge*3 Terminate Burst, Latch CA, ...

Page 9

... BA, CA, A10 BA, A10 Op-Code Mode-Add MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM Command Action DESEL NOP (Idle after tRP) NOP NOP (Idle after tRP) TBST ILLEGAL*2 READ / WRITE ILLEGAL*2 ACT ILLEGAL*2 PRE / PREA NOP*4 (Idle after tRP) ...

Page 10

... X BA, CA, A10 BA, A10 Op-Code Mode-Add MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM Command Action DESEL NOP (Idle after tRC) NOP NOP (Idle after tRC) TBST ILLEGAL READ / WRITE ILLEGAL ACT ILLEGAL PRE / PREA ILLEGAL REFA ILLEGAL ...

Page 11

... MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM Add Action X INVALID X Exit Self-Refresh (Idle after tRC) X Exit Self-Refresh (Idle after tRC) X ILLEGAL X ILLEGAL X ILLEGAL X NOP (Maintain Self-Refresh) X INVALID X Exit Power Down to Idle ...

Page 12

... TBST WRITE WRITEA READA READ WRITE WRITE WRITEA WRITEA READA PRE WRITEA PRE PRE PRE PRE CHARGE ON MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM SELF REFRESH REFSX REFA AUTO REFRESH CKEL POWER DOWN TBST READ CKEL READ READ SUSPEND CKEH READA ...

Page 13

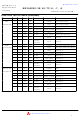

... R: Reserved for Future Use M2V56S20/ 30/ 40/ TP -6, - LTMODE 0 Burst Write 1 Single Write MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM CLK /CS /RAS /CAS /WE BA0,1 A12- BT BURST ...

Page 14

... MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM Write Burst Length Burst Type Interleaved ...

Page 15

... BL after READA. The next ACT command can be issued after (BL + tRP) from the previous READA. In any case, tRCD+BL M2V56S20/ 30/ 40/ TP -6, -7, -8 ACT READ tRCD MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM PRE ACT tRP Qb0 Qb1 Qb2 Qb3 Precharge All tRASmin must be met ...

Page 16

... Qa1 Qa2 READ Qa0 Qa1 Qa2 internal precharge starts READ BL Qa0 Qa1 Qa2 Qa0 Qa1 internal precharge starts MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM PRE ACT tRP Qa3 Qb0 Qb1 Qb2 ACT tRP Xa Xa ...

Page 17

... M2V56S20/ 30/ 40/ TP -6, -7, -8 Write (BL=4) Write Da0 Da1 Da2 Da3 Write with Auto-Precharge (BL=4) Write Da0 Da1 Da2 Da3 internal precharge starts MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM PRE ACT tRP tWR ACT tRP tWR 17 ...

Page 18

... Read interrupted by Write (CL=2, BL=4) CLK Command ACT A0-9,11-12 Xa A10 Xa BA0-1 00 DQM DQ READ READ Qa0 Qa1 Qa2 Qb0 READ Write Qa0 Da0 Output disable by DQM MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM Qc0 Qc1 Qc2 Qc3 Da1 Da2 Da3 by WRITE 18 ...

Page 19

... A PRE command to output disable latency is equivalent to the /CAS Latency. CLK Command DQ Command CL=2 DQ Command DQ Command DQ Command CL=3 DQ Command DQ M2V56S20/ 30/ 40/ TP -6, -7, -8 Read interrupted by Precharge (BL=4) READ PRE Q0 Q1 READ PRE Q0 Q1 READ PRE Q0 READ PRE Q0 READ PRE Q0 READ PRE Q0 MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM ...

Page 20

... CLK. A TBST command to output disable latency is equivalent to the /CAS Latency. CLK Command DQ Command CL=2 DQ Command DQ Command DQ Command CL=3 DQ Command DQ M2V56S20/ 30/ 40/ TP -6, -7, -8 Read interrupted by Terminate (BL=4) READ TBST Q0 Q1 READ TBST Q0 Q1 READ TBST Q0 READ TBST Q0 READ TBST Q0 READ TBST Q0 MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM ...

Page 21

... BA0 M2V56S20/ 30/ 40/ TP -6, -7, -8 Write Write Da1 Da2 Db0 Dc0 Write interrupted by Read (CL=2, BL=4) Write READ Da0 Da1 don't care MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM Dc1 Dc2 Dc3 Qb0 Qb1 Qb2 Qb3 21 ...

Page 22

... Write interrupted by Terminate (BL=4) CLK Command ACT A0-9,11-12 Xa A10 0 BA0 M2V56S20/ 30/ 40/ TP -6, -7, -8 Write tWR Da0 Da1 Write TBST Da0 Da1 MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM PRE ACT tRP Write Db0 Db1 Db2 Db3 22 ...

Page 23

... Da0 auto-precharge M2V56S20/ 30/ 40/ TP -6, -7, -8 Write BL Yb tWR 0 10 Da1 Db0 Db1 Db2 interrupted Read BL Yb tWR 0 10 Da1 Qb0 interrupted MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM ACT tRP Db3 activate ACT tRP Qb1 Qb2 Qb3 activate 23 ...

Page 24

... Single Write When sigle write mode is set, burst length for write is always one, independently of Burst Length defined by (A2-0). M2V56S20/ 30/ 40/ TP -6, -7, -8 Read Qa0 Qa1 Qb0 interrupted MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM ACT tRP Qb1 Qb2 Qb3 activate 24 ...

Page 25

... Auto-refresh to auto-refresh interval is minimum tRFC. Any command must not be issued before tRFC from the REFA command. CLK /CS /RAS /CAS /WE CKE A0-12 BA0-1 Auto Refresh on All Banks M2V56S20/ 30/ 40/ TP -6, -7, -8 Auto-Refresh NOP or DESELECT minimum tRFC MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM Auto Refresh on All Banks 25 ...

Page 26

... DESEL or NOP commands must be asserted till then. CLK /CS /RAS /CAS /WE CKE A0-12 BA0-1 Self Refresh Entry M2V56S20/ 30/ 40/ TP -6, -7, -8 Self-Refresh Stable CLK MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM NOP new command Self Refresh Exit minimum tRFC for recovery ...

Page 27

... CLK CKE Command Write D0 DQ M2V56S20/ 30/ 40/ TP -6, -7, -8 tIH tIS tIH tIS Power Down by CKE NOP NOP NOP NOP NOP NOP DQ Suspend by CKE MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM Standby Power Down Active Power Down Read ...

Page 28

... During writes, DQMU/L masks input data word by word. DQMU/L to Data In latency is 0. During reads, DQMU/L forces output to Hi-Z word by word. DQMU/L to output Hi-Z latency is 2. CLK Command Write DQMU masked by DQMU/L=H DQM Function Read D2 D3 MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM disabled by DQMU/L=H 28 ...

Page 29

... Vss with respect to VssQ with respect to Vss with respect to VssQ Parameter Min. 3.0 0 3.0 0 2.0 -0.3 0.3V, Vss = VssQ = 0V, unless otherwise noted) Parameter Test Condition VI=1.4v f=1MHz VI=25mVrms MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM Ratings Unit -0.5 ~ 4.6 V -0.5 ~ 4.6 V -0.5 ~ Vdd+0.5 V -0.5 ~ VddQ+0 1000 -65 ~ 150 C ...

Page 30

... CKE VIHmin tCLK=min, BL=4, gapless data tCLK=min, tRFC=min CKE 0.2v -6/-7/-8 0.3V, Vss = VssQ = 0V, unless otherwise noted) Test Conditions IOH=-2mA IOL= 2mA Q floating Vo=0 ~ VddQ VIH=0 ~ VddQ+0.3V, other input pins=0V MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM Limits(max) Organiz Unit 133 100 ation MHz MHz x4 90 ...

Page 31

... M2V56S20/ 30/ 40/ TP -6, -7, -8 0.3V, Vss = VssQ = 0V, unless otherwise noted) 0.8V to 2.0V 1.4V -6 Min. Max. CL=2 10 CL=3 7.5 2.5 2 1.5 0.8 67 120000 7.8 1.4V 1.4V MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM Limits -7 -8 Min. Max. Min. Max ...

Page 32

... Output Load Condition Vout CLK DQ tOLZ tAC M2V56S20/ 30/ 40/ TP -6, -7, -8 0.3V, Vss = VssQ = 0V, unless otherwise noted) -6 Min. CL=2 CL=3 CL 50pF 1.4V 1.4V tOHZ tOH MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM Limits -7 -8 Max Min. Max Min. Max ...

Page 33

... A12 X BA0 ACT#0 WRITE tRC tRAS tRP tWR PRE#0 MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM tRCD ACT#0 WRITE#0 Italic paramater shows minimum case 16 tWR 0 PRE#0 ...

Page 34

... PRE#0 ACT#1 WRITEA#1 (Auto-Precharge) MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM tRCD ACT#0 WRITE#0 ACT#1 Italic paramater shows minimum case ...

Page 35

... A12 X BA0 ACT#0 READ tRC tRAS tRP PRE#0 ACT#0 MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM tRAS tRCD READ#0 PRE#0 Italic paramater shows minimum case ...

Page 36

... ACT#0 ACT#1 READA#1 MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM tRAS tRCD READ#0 PRE#0 ACT#1 Italic paramater shows minimum case ...

Page 37

... WRITE#0 WRITEA#1 interrupt interrupt same bank other bank MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM tWR WRITE#0 PRE#0 interrupt other bank Italic paramater shows minimum case 16 X ...

Page 38

... READ#1 READA#1 interrupt interrupt ACT#1 other bank same bank MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM READ#0 interrupt ACT#1 other bank Italic paramater shows minimum case ...

Page 39

... DQM A0-9,11 X A10 X A12 X BA0 ACT#0 ACT tRCD WRITE#0 READ#1 MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM tWR WRITE#1 PRE#1 Italic paramater shows minimum case ...

Page 40

... DQ D0 ACT#0 WRITE tRP tRCD tWR ACT#0 PRE#0 Terminate MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM tRC tRAS tRP READ#0 PRE#0 ACT#0 Terminate Italic paramater shows minimum case ...

Page 41

... A12 X BA0 ACT#0 WRITE#0 M2V56S20/ 30/ 40/ TP -6, - READ#0 TBST TBST MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM tWR WRITE#0 Italic paramater shows minimum case 16 0 PRE#0 41 ...

Page 42

... CKE DQM A0-9,11 X A10 X A12 X BA0 ACT#0 WRITE#0 M2V56S20/ 30/ 40/ TP -6, - READ#0 MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM Italic paramater shows minimum case 16 42 ...

Page 43

... CKE DQM A0-9,11 A10 A12 BA0,1 DQ NOP Power On PRE ALL tRP tRFC REFA REFA Minimum 8 REFA cycles Italic paramater shows minimum case MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM tRFC tRSC REFA MRS ACT#0 43 ...

Page 44

... CKE DQM A0-9,11 A10 A12 BA0,1 DQ PRE ALL REFA All banks must be idle before REFA is issued. M2V56S20/ 30/ 40/ TP -6, - tRFC MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM tRCD ACT#0 ...

Page 45

... A0-9,11 A10 A12 BA0,1 DQ PRE ALL Self Refresh Entry All banks must be idle before REFS is issued Italic paramater shows minimum case MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM tRFC Self Refresh Exit ACT ...

Page 46

... CKE DQM A0-9,11 X A10 X A12 X BA0 ACT#0 WRITE internal CLK READ#0 suspended MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM internal CLK suspended Italic paramater shows minimum case 16 46 ...

Page 47

... CKE DQM A0-9,11 A10 A12 BA0,1 DQ PRE ALL M2V56S20/ 30/ 40/ TP -6, - Standby Power Down ACT#0 MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM Active Power Down Italic paramater shows minimum case ...

Page 48

... Icc5 Limits (from 160/150mA to 180/170mA) Icc6 Test Condition (CKE 0.2V) Icc6 Limits (from 2mA to 3mA) - Change Switching Characteristics tAC of -8 for CL=2 from 6ns to 7ns - Add Note to Switching Characteristics - Change Output Load Condition to 50pF only - Remove tCCD from AC Timing Requirements MITSUBISHI ELECTRIC MITSUBISHI LSIs 256M Synchronous DRAM 48 ...

Page 49

... Notes regarding these materials 1. These materials are intended as a reference to assist our customers in the selection of the Mitsubishi semiconductor product best suited to the customer’s application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Mitsubishi Electric Corporation or a third party ...