K4D26323RA-GC33 Samsung, K4D26323RA-GC33 Datasheet

K4D26323RA-GC33

Specifications of K4D26323RA-GC33

Available stocks

Related parts for K4D26323RA-GC33

K4D26323RA-GC33 Summary of contents

Page 1

... K4D26323RA-GC 128Mbit DDR SDRAM Double Data Rate Synchronous RAM with Bi-directional Data Strobe and DLL Samsung Electronics reserves the right to change products or specification without notice. * VDD / VDDQ=2. 32Bit x 4 Banks (144-Ball FBGA) Revision 2.0 January 2003 - 1 - 128M DDR SDRAM Rev. 2.0 (Jan. 2003) ...

Page 2

... Changed tRCDRD of K4D26323RA-GC33 from 6tCK to 4tCK • Changed tRCDWR of K4D26323RA-GC33 from 4tCK to 2tCK • Changed tRP of K4D26323RA-GC33 from 5tCK to 4tCK • Changed tWR of K4D26323RA-GC33 from 3tCK to 2tCK • Changed tDAL of K4D26323RA-GC33 from 8tCK to 7tCK Revision 1.8 (July 18, 2002) • Changed power dissipation from 2,0W to 3.3W Revision 1.7 (May 7, 2002) • ...

Page 3

... K4D26323RA-GC Revision 1.2 (September 13, 2001) • Define DC spec value of K4D26323RA-GC33 and K4D263238A-GC2A • Changed tCK(max) of -2A and -33 from 7ns to 5ns Revision 1.1 (September 3, 2001) • Added K4D26323RA-GC33(VDD/VDDQ=2.8V) • Added K4D263238A-GC2A(350MHz) Revision 1.0 (August 16, 2001) • Changed tCDLR of K4D263238A-GC33 from 2tCK to 3tCK • Removed VDDQ=1.8V from the spec. ...

Page 4

... Differential clock input • No Wrtie-Interrupted by Read Function ORDERING INFORMATION Part NO. K4D26323RA-GC2A K4D26323RA-GC33 K4D26323RA-GC36 GENERAL DESCRIPTION FOR 1M x 32Bit x 4 Bank DDR SDRAM The K4D26323RA is 134,217,728 bits of hyper synchronous data rate Dynamic RAM organized as 4 x1,048,576 words by 32 bits, fabricated with SAMSUNG ’ ...

Page 5

... K4D26323RA-GC PIN CONFIGURATION (Top View DQS0 DM0 VSSQ C DQ4 VDDQ NC D DQ6 DQ5 VSSQ E DQ7 VDDQ VDD F DQ17 DQ16 VDDQ G DQ19 DQ18 VDDQ DQS2 DM2 NC H DQ21 DQ20 VDDQ J DQ22 DQ23 VDDQ K CAS WE VDD L RAS BA0 N NOTE: 1 ...

Page 6

... K4D26323RA-GC INPUT/OUTPUT FUNCTIONAL DESCRIPTION Symbol Type CK, CK*1 Input CKE Input CS Input RAS Input CAS Input WE Input DQS ~ DQS Input/Output Input Input/Output Input Input Power Supply Power Supply DDQ SSQ V Power Supply ...

Page 7

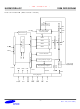

... K4D26323RA-GC BLOCK DIAGRAM (1Mbit x 32I Bank) Bank Select CK,CK ADDR LCKE LRAS LCBR CK,CK CKE * VDD / VDDQ=2. Intput Buffer CK, CK Data Input Register Serial to parallel 64 1Mx32 1Mx32 1Mx32 1Mx32 Column Decoder Latency & Burst Length Programming Register LWE LCAS LWCBR Timing Register ...

Page 8

... K4D26323RA-GC FUNCTIONAL DESCRIPTION • Power-Up Sequence DDR SDRAMs must be powered up and initialized in a predefined manner to prevent undefined operations. 1. Apply power and keep CKE at low state (All other inputs may be undefined) - Apply VDD before VDDQ . - Apply VDDQ before VREF & VTT 2. Start clock and maintain stable condition for minimum 200us. ...

Page 9

... K4D26323RA-GC MODE REGISTER SET(MRS) The mode register stores the data for controlling the various operating modes of DDR SDRAM. It programs CAS latency, addressing mode, burst length, test mode, DLL reset and various vendor specific options to make DDR SDRAM useful for variety of different applications. The default value of the mode register is not defined, therefore the mode register must be written after EMRS setting for proper operation ...

Page 10

... K4D26323RA-GC EXTENDED MODE REGISTER SET(EMRS) The extended mode register stores the data for enabling or disabling DLL and selecting output driver strength. The default value of the extended mode register is not defined, therefore the extened mode register must be written after power up for enabling or disabling DLL. The extended mode register is written by assert- ing low on CS, RAS, CAS, WE and high on BA0(The DDR SDRAM should be in all bank precharge with CKE already high prior to writing into the extended mode register) ...

Page 11

... IH DDQ 5. V (mim.)= -1.5V for a pulse width and it can not be greater than 1/3 of the cycle rate For any pin under test input of 0V < For K4D26323RA-GC2A/33/36 VDD / VDDQ=2.8V * Symbol OUT ...

Page 12

... K4D26323RA-GC DC CHARACTERISTICS Recommended operating conditions Unless Otherwise Noted, T Parameter Symbol Operating Current I CC1 (One Bank Active) Precharge Standby Current I P CC2 in Power-down mode Precharge Standby Current I N CC2 in Non Power-down mode Active Standby Current I P CC3 power-down mode Active Standby Current in ...

Page 13

... K4D26323RA-GC AC OPERATING TEST CONDITIONS Parameter Input reference voltage for CK(for single ended) CK and CK signal maximum peak swing CK signal minimum slew rate Input Levels Input timing measurement reference level Output timing measurement reference level Output load condition Output CAPACITANCE (V =2.5V Parameter ...

Page 14

... K4D26323RA-GC AC CHARACTERISTICS Sym- Parameter bol CL cycle time CK CL high level width low level width CL t DQS out access time from CK DQSCK t Output access time from Data strobe edge to Dout edge DQSQ t Read preamble RPRE t Read postamble RPST valid DQS-in ...

Page 15

... K4D26323RA-GC Note The JEDEC DDR specification currently defines the output data valid window(tDV) as the time period when the data strobe and all data associated with that data strobe are coincidentally valid. - The previously used definition of tDV(=0.35tCK) artificially penalizes system timing budgets by assuming the worst case ...

Page 16

... REF Note : 1. For normal write operation, even numbers of Din are to be written inside DRAM AC CHARACTERISTICS (II) K4D26323RA-GC2A Frequency Cas Latency 350MHz ( 2.86ns ) 4 300MHz ( 3.3ns ) 4 275MHz ( 3.6ns ) 4 K4D26323RA-GC33 Frequency Cas Latency 300MHz ( 3.3ns ) 4 275MHz ( 3.6ns ) 4 K4D26323RA-GC36 Frequency Cas Latency 275MHz ( 3.6ns ) 4 * VDD / VDDQ=2.8V * ...

Page 17

... K4D26323RA-GC Simplified Timing( ...

Page 18

... K4D26323RA-GC PACKAGE DIMENSIONS (144-Ball FBGA) 0.10 Max 0.45 ± 0.05 0.35 1.40 * VDD / VDDQ=2. INDEX MARK 12.0 <Top View> 0.8x11=8.8 0 ± 0.05 0.40 Max <Bottom View> 128M DDR SDRAM 12.0 A1 INDEX MARK 0.8 0.40 Unit : mm Rev. 2.0 (Jan. 2003) ...