CP82C59A-12 Intersil, CP82C59A-12 Datasheet - Page 4

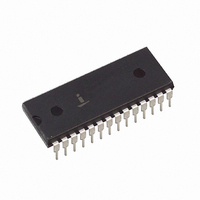

CP82C59A-12

Manufacturer Part Number

CP82C59A-12

Description

IC INTERFACE 5V 12.5MHZ 28-DIP

Manufacturer

Intersil

Datasheet

1.CS82C59AZ.pdf

(22 pages)

Specifications of CP82C59A-12

Controller Type

CMOS Priority Interrupt Controller

Voltage - Supply

4.5 V ~ 5.5 V

Current - Supply

1mA

Operating Temperature

0°C ~ 70°C

Mounting Type

Through Hole

Package / Case

28-DIP (0.600", 15.24mm)

Supply Voltage Range

4.5V To 5.5V

Supply Current

1mA

Digital Ic Case Style

DIP

No. Of Pins

28

Operating Temperature Range

0°C To +70°C

Filter Terminals

Through Hole

Rohs Compliant

No

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Interface

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Pin Description

Functional Description

Interrupts in Microcomputer Systems

Microcomputer system design requires that I/O devices such

as keyboards, displays, sensors and other components

receive servicing in an efficient manner so that large

amounts of the total system tasks can be assumed by the

microcomputer with little or no effect on throughput.

The most common method of servicing such devices is the

Polled approach. This is where the processor must test each

device in sequence and in effect “ask” each one if it needs

servicing. It is easy to see that a large portion of the main

program is looping through this continuous polling cycle and

that such a method would have a serious, detrimental effect

on system throughput, thus, limiting the tasks that could be

assumed by the microcomputer and reducing the cost

effectiveness of using such devices.

CAS0 - CAS2

SYMBOL

IR0 - IR7

D7 - D0

SP/EN

GND

INTA

V

WR

INT

RD

CS

A0

CC

TYPE

I/O

I/O

I/O

O

I

I

I

I

I

I

I

I

V

GROUND

CHIP SELECT: A low on this pin enables RD and WR communications between the CPU and the 82C59A. INTA

functions are independent of CS.

WRITE: A low on this pin when CS is low enables the 82C59A to accept command words from the CPU.

READ: A low on this pin when CS is low enables the 82C59A to release status onto the data bus for the CPU.

BIDIRECTIONAL DATA BUS: Control, status, and interrupt-vector information is transferred via this bus.

CASCADE LINES: The CAS lines form a private 82C59A bus to control a multiple 82C59A structure. These

pins are outputs for a master 82C59A and inputs for a slave 82C59A.

SLAVE PROGRAM/ENABLE BUFFER: This is a dual function pin. When in the Buffered Mode it can be used

as an output to control buffer transceivers (EN). When not in the Buffered Mode it is used as an input to

designate a master (SP = 1) or slave (SP = 0).

INTERRUPT: This pin goes high whenever a valid interrupt request is asserted. It is used to interrupt the CPU,

thus, it is connected to the CPU's interrupt pin.

INTERRUPT REQUESTS: Asynchronous inputs. An interrupt request is executed by raising an IR input (low to

high), and holding it high until it is acknowledged (Edge Triggered Mode), or just by a high level on an IR input

(Level Triggered Mode). Internal pull-up resistors are implemented on IR0 - 7.

INTERRUPT ACKNOWLEDGE: This pin is used to enable 82C59A interrupt-vector data onto the data bus by

a sequence of interrupt acknowledge pulses issued by the CPU.

ADDRESS LINE: This pin acts in conjunction with the CS, WR, and RD pins. It is used by the 82C59A to

decipher various Command Words the CPU writes and status the CPU wishes to read. It is typically connected

to the CPU A0 address line (A1 for 80C86/88/286).

CC

: The +5V power supply pin. A 0.1µF capacitor between pins 28 and 14 is recommended for decoupling.

4

82C59A

82C59A

DESCRIPTION

RAM

ROM

FIGURE 2. POLLED METHOD

CPU

I/O (N)

I/O (1)

I/O (2)

MULTIPLEXER

CPU - DRIVEN

March 17, 2006

FN2784.5