LTC1955EUH Linear Technology, LTC1955EUH Datasheet - Page 14

LTC1955EUH

Manufacturer Part Number

LTC1955EUH

Description

IC INTERFACE DL SMART CARD 32QFN

Manufacturer

Linear Technology

Datasheet

1.LTC1955EUHPBF.pdf

(20 pages)

Specifications of LTC1955EUH

Controller Type

Smart Card Interface

Interface

4-Wire Serial

Voltage - Supply

1.7 V ~ 5.5 V

Current - Supply

10µA

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

32-QFN

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LTC1955EUH

Manufacturer:

LT

Quantity:

10 000

Part Number:

LTC1955EUH

Manufacturer:

LINEAR/凌特

Quantity:

20 000

Company:

Part Number:

LTC1955EUH#PBF

Manufacturer:

ADI

Quantity:

5

Part Number:

LTC1955EUH#PBF

Manufacturer:

LINEAR/凌特

Quantity:

20 000

Part Number:

LTC1955EUH#TRPBF

Manufacturer:

LINEAR/凌特

Quantity:

20 000

APPLICATIONS INFORMATION

LTC1955

10kV ESD Protection

All smart card pins (CLK A/CLK B, RST A/RST B, I/O A/I/O B,

C4A, C8A and V

human body model ESD in-situ. In order to ensure proper

ESD protection, careful board layout is required. The

PGND and SGND pins should be tied directly to a ground

plane. The V

close to the V

ground plane.

Capacitor Selection

Warning: A polarized capacitor such as tantalum or alumi-

num should never be used for the fl ying capacitor since

its voltage can reverse upon start-up of the LTC1955.

Low ESR ceramic capacitors should always be used for

the fl ying capacitor.

A total of six capacitors are required to operate the LTC1955.

An input bypass capacitor is required at PV

and DV

of the smart card V

capacitor is required from C

capacitor is required on the charge pump out pin CPO.

To prevent excessive noise spikes due to charge pump

operation, low ESR (equivalent series resistance) multi-

layer ceramic capacitors are strongly recommended.

There are several types of ceramic capacitors available, each

having considerably different characteristics. For example,

X7R/X5R ceramic capacitors have excellent voltage and

temperature stability but relatively low packing density.

Y5V ceramic capacitors have apparently higher packing

density but poor performance over their rated voltage or

temperature ranges. Under certain voltage and temperature

conditions, Y5V and X7R/X5R ceramic capacitors can be

compared directly by case size rather than specifi ed value

for a desired minimum capacitance.

Placement of the capacitors is critical for correct operation

of the LTC1955. Because the charge pump generates large

current steps, all of the capacitors should be placed as close

to the LTC1955 as possible. The low impedance nature of

multilayer ceramic chip capacitors will minimize voltage

spikes but only if the power path is kept very short (i.e.,

minimum inductance). The PV

14

CC

. Output bypass capacitors are required on each

CCA

CCA

/V

CCA

/V

CCB

CCB

CCA

/V

capacitors should be located very

CCB

/V

pins and tied immediately to the

CCB

) can withstand over 10kV of

+

pins. A charge pump fl ying

to C

BATT

–

/SV

and a charge storage

BATT

nodes should

BATT

, SV

BATT

be especially well bypassed. The capacitor for this node

should be directly adjacent to the QFN package. The CPO

and fl ying capacitors should be very close as well. The

LTC1955 can tolerate more distance between the LDO

capacitors and the V

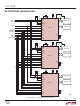

Figure 3 shows an example of a tight printed circuit

board using single-layer copper. For best performance, a

multilayer board can be used and should employ a solid

ground plane on at least one layer.

The following capacitors are recommended for use with

the LTC1955.

C

CPO

C

V

CDV

IN

FLY

CCA/B

CC

Figure 3. Optimum Single-Layer PCB Layout

V

TYPE

CCA

X5R

X5R

X5R

VALUE

4.7μF

0.1μF

GND

1μF

CCA/B

CASE SIZE MURATA P/N

pins.

0805

0603

0402

V

BATT

GRM40-034 X5R 475K 6.3

GRM39 X5R 105K 6.3

GRM36 X5R 104K 10

V

CCB

1955 F03

1955fb