EP1C4F400C7 Altera, EP1C4F400C7 Datasheet - Page 69

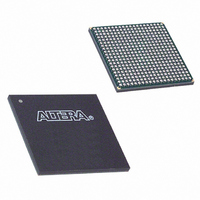

EP1C4F400C7

Manufacturer Part Number

EP1C4F400C7

Description

IC CYCLONE FPGA 4K LE 400-FBGA

Manufacturer

Altera

Series

Cyclone®r

Datasheet

1.EP1C3T144C8.pdf

(106 pages)

Specifications of EP1C4F400C7

Number Of Logic Elements/cells

4000

Number Of Labs/clbs

400

Total Ram Bits

78336

Number Of I /o

301

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

400-FBGA

Family Name

Cyclone®

Number Of Logic Blocks/elements

4000

# I/os (max)

301

Frequency (max)

320.1MHz

Process Technology

0.13um (CMOS)

Operating Supply Voltage (typ)

1.5V

Logic Cells

4000

Ram Bits

78336

Operating Supply Voltage (min)

1.425V

Operating Supply Voltage (max)

1.575V

Operating Temp Range

0C to 85C

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

400

Package Type

FBGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Lead Free Status / Rohs Status

Not Compliant

Other names

544-2079

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP1C4F400C7

Manufacturer:

TI

Quantity:

150

Company:

Part Number:

EP1C4F400C7

Manufacturer:

ALTERA

Quantity:

3 000

Company:

Part Number:

EP1C4F400C7N

Manufacturer:

ALTERA

Quantity:

784

Part Number:

EP1C4F400C7N

Manufacturer:

ALTERA

Quantity:

20 000

Referenced

Documents

Document

Revision History

Altera Corporation

May 2008

May 2008

v1.4

January 2007

v1.3

August 2005

V1.2

February 2005

V1.1

May 2003 v1.0

Table 3–6. Document Revision History

Document

Date and

Version

Added document to Cyclone Device Handbook.

Minor textual and style changes. Added

Documents”

●

●

Minor updates.

Updated JTAG chain limits. Added information concerning test

vectors.

Added document revision history.

Updated handpara note below

Multiple Cyclone devices can be configured in any of the three

configuration schemes by connecting the configuration enable (nCE) and

configuration enable output (nCEO) pins on each device.

This chapter references the following document:

■

■

Table 3–6

Active serial

Passive serial (PS)

JTAG

section.

Table 3–5. Data Sources for Configuration

Configuration Scheme

AN 39: IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices

Jam Programming & Test Language Specification

shows the revision history for this chapter.

Changes Made

Table

“Referenced

3–4.

Low-cost serial configuration device

Enhanced or EPC2 configuration device,

MasterBlaster or ByteBlasterMV download cable,

or serial data source

MasterBlaster or ByteBlasterMV download cable

or a microprocessor with a Jam or JBC file

Data Source

Referenced Documents

Summary of Changes

—

—

—

—

—

Preliminary

3–7