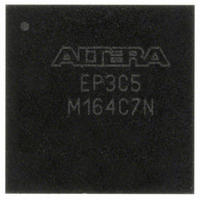

EP3C5M164C7N Altera, EP3C5M164C7N Datasheet - Page 53

EP3C5M164C7N

Manufacturer Part Number

EP3C5M164C7N

Description

IC CYCLONE III FPGA 5K 164 MBGA

Manufacturer

Altera

Series

Cyclone® IIIr

Datasheets

1.EP3C5F256C8N.pdf

(5 pages)

2.EP3C5F256C8N.pdf

(34 pages)

3.EP3C5F256C8N.pdf

(66 pages)

4.EP3C5F256C8N.pdf

(14 pages)

5.EP3C5F256C8N.pdf

(76 pages)

6.EP3C5M164C7N.pdf

(274 pages)

Specifications of EP3C5M164C7N

Number Of Logic Elements/cells

5136

Number Of Labs/clbs

321

Total Ram Bits

423936

Number Of I /o

106

Voltage - Supply

1.15 V ~ 1.25 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

164-MBGA

Family Name

Cyclone III

Number Of Logic Blocks/elements

5136

# I/os (max)

106

Frequency (max)

437.5MHz

Process Technology

65nm

Operating Supply Voltage (typ)

1.2V

Logic Cells

5136

Ram Bits

423936

Operating Supply Voltage (min)

1.15V

Operating Supply Voltage (max)

1.25V

Operating Temp Range

0C to 85C

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

164

Package Type

MBGA

For Use With

544-2601 - KIT DEV CYCLONE III LS EP3CLS200544-2411 - KIT DEV NIOS II CYCLONE III ED.

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Lead Free Status / Rohs Status

Compliant

Other names

544-2559

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP3C5M164C7N

Manufacturer:

ALTERA

Quantity:

526

Verification

Figure 13. Specifying the Number of Processors

© November 2008 Altera Corporation

f

Preserving Performance

You can use the incremental compilation feature to preserve unchanged parts of your

design, thus preserving performance and allowing you to reach timing closure more

efficiently. For guidelines and references, refer to

Team-Based Design” on page

Reducing Compilation Time

You can speed up design iteration time by an average of 60% when making changes to

the design with the incremental compilation feature.

For guidelines and references, refer to the

Design” on page

The Quartus II software can run some algorithms in parallel to take advantage of

multiple processors and reduce compilation time when more than one processor is

available to compile the design. To set the number of processors available for a

Quartus II compilation, specify the Maximum processors allows for parallel

compilation on the Compilation Process Settings page of the Settings dialog box, as

in

parallel compilation.

Figure

13. The default value for the number of processors is 1, which disables

35.

35.

“Planning for Hierarchical and Team-Based

“Planning for Hierarchical and

Page 53