EP1K100FC484-3N Altera, EP1K100FC484-3N Datasheet - Page 20

EP1K100FC484-3N

Manufacturer Part Number

EP1K100FC484-3N

Description

IC ACEX 1K FPGA 100K 484-FBGA

Manufacturer

Altera

Series

ACEX-1K®r

Datasheet

1.EP1K10TC100-3N.pdf

(86 pages)

Specifications of EP1K100FC484-3N

Number Of Logic Elements/cells

4992

Number Of Labs/clbs

624

Total Ram Bits

49152

Number Of I /o

333

Number Of Gates

257000

Voltage - Supply

2.375 V ~ 2.625 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

484-FBGA

Logic Type

Programmable Logic Device (PLD)

No. Of I/o's

333

Frequency

180MHz

Supply Current Max

25mA

Operating Temperature Range

0°C To +70°C

Logic Case Style

BGA

No. Of Pins

484

Rohs Compliant

Yes

Clock Management

PLL

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

544-2368

EP1K100FC484-3N

EP1K100FC484-3N

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP1K100FC484-3N

Manufacturer:

ALTERA

Quantity:

1 831

Company:

Part Number:

EP1K100FC484-3N

Manufacturer:

ALTERA32

Quantity:

405

Part Number:

EP1K100FC484-3N

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

ACEX 1K Programmable Logic Device Family Data Sheet

20

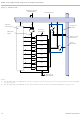

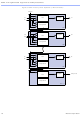

LE Operating Modes

The ACEX 1K LE can operate in the following four modes:

Each of these modes uses LE resources differently. In each mode, seven

available inputs to the LE—the four data inputs from the LAB local

interconnect, the feedback from the programmable register, and the

carry-in and cascade-in from the previous LE—are directed to different

destinations to implement the desired logic function. Three inputs to the

LE provide clock, clear, and preset control for the register. The Altera

software, in conjunction with parameterized functions such as LPM and

DesignWare functions, automatically chooses the appropriate mode for

common functions such as counters, adders, and multipliers. If required,

the designer can also create special-purpose functions that use a specific

LE operating mode for optimal performance.

The architecture provides a synchronous clock enable to the register in all

four modes. The Altera software can set DATA1 to enable the register

synchronously, providing easy implementation of fully synchronous

designs.

Figure 11

Normal mode

Arithmetic mode

Up/down counter mode

Clearable counter mode

shows the ACEX 1K LE operating modes.

Altera Corporation