ADC08238CIN National Semiconductor, ADC08238CIN Datasheet - Page 17

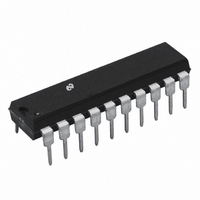

ADC08238CIN

Manufacturer Part Number

ADC08238CIN

Description

IC ADC 8BIT NS SERIAL I/O 20-DIP

Manufacturer

National Semiconductor

Datasheet

1.ADC08231BIN.pdf

(24 pages)

Specifications of ADC08238CIN

Number Of Bits

8

Sampling Rate (per Second)

286k

Data Interface

NSC MICROWIRE™, Serial

Number Of Converters

1

Power Dissipation (max)

20mW

Voltage Supply Source

Single Supply

Operating Temperature

-40°C ~ 85°C

Mounting Type

Through Hole

Package / Case

20-DIP (0.300", 7.62mm)

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

*ADC08238CIN

Functional Description

4 0 THE ANALOG INPUTS

The most important feature of these converters is that they

can be located right at the analog signal source and through

just a few wires can communicate with a controlling proces-

sor with a highly noise immune serial bit stream This in itself

greatly minimizes circuitry to maintain analog signal accura-

cy which otherwise is most susceptible to noise pickup

However a few words are in order with regard to the analog

inputs should the input be noisy to begin with or possibly

riding on a large common-mode voltage

The differential input of these converters actually reduces

the effects of common-mode input noise a signal common

to both selected ‘‘

(60 Hz is most typical) The time interval between sampling

the ‘‘

od The change in the common-mode voltage during this

short time interval can cause conversion errors For a sinus-

oidal common-mode signal this error is

where f

For a 60Hz common-mode signal to generate a

ror (

value would have to be 6 63V which would be larger than

allowed as it exceeds the maximum analog input limits

Source resistance limitation is important with regard to the

DC leakage currents of the input multiplexer While operat-

ing near or at maximum speed bypass capacitors should

not be used if the source resistance is greater than 1k

The worst-case leakage current of

will create a 1mV input error with a 1k

An op amp RC active low pass filter can provide both im-

pedance buffering and noise filtering should a high imped-

ance signal source be required

5 0 OPTIONAL ADJUSTMENTS

5 1 Zero Error

The zero of the A D does not require adjustment If the

minimum analog input voltage value V

a zero offset can be done The converter can be made to

output 0000 0000 digital code for this minimum input voltage

by biasing any V

utilizes the differential mode operation of the A D

and f

V

PEAK

a

5mV) with the converter running at 250kHz its peak

’’ input and then the ‘‘

CLK

CM

is its peak voltage value

V

is the frequency of the common-mode signal

is the A D clock frequency

error

(max)

IN

a

(

b

’’ and ‘‘

e

) input at this V

V

PEAK

b

b

’’ input is

(2 f

’’ inputs for a conversion

g

CM

1 A over temperature

IN(MIN)

(Continued)

)

IN(MIN)

source resistance

f

0 5

CLK

of a clock peri-

is not ground

value This

LSB er-

17

The zero error of the A D converter relates to the location

of the first riser of the transfer function and can be mea-

sured by grounding the V

magnitude positive voltage to the V

is the difference between the actual DC input voltage which

is necessary to just cause an output digital code transition

from 0000 0000 to 0000 0001 and the ideal

(

5 2 Full Scale

A full-scale adjustment can be made by applying a differen-

tial input voltage which is 1

analog full-scale voltage range and then adjusting the mag-

nitude of the V

just changing from 1111 1110 to 1111 1111 (See figure enti-

tled ‘‘Span Adjust 0V

with the ADC08234 and ADC08238 (The reference is inter-

nally connected to V

5 3 Adjusting for an Arbitrary Analog Input

Voltage Range

If the analog zero voltage of the A D is shifted away from

ground (for example to accommodate an analog input sig-

nal which does not go to ground) this new zero reference

should be properly adjusted first A V

equals this desired zero reference plus

LSB is calculated for the desired analog span using 1 LSB

the zero reference voltage at the corresponding ‘‘

should then be adjusted to just obtain the 00

code transition

The full-scale adjustment should be made with the proper

V

input which is given by

where

and

The V

code change from FE

justment procedure

e

IN

V

V

V

analog span 256) is applied to selected ‘‘

LSB

IN

MAX

MIN

(

b

(

REF

) voltage applied by forcing a voltage to the V

a

e

e

e

) fs adj

IN (or V

the low end (the offset zero) of the analog range

(Both are ground referenced )

the high end of the analog input range

9 8mV for V

REF

e

CC

IN input for a digital output code which is

V

) voltage is then adjusted to provide a

REF

MAX

HEX

s

REF

IN of the ADC08231)

b

IN

V

to FF

IN s

1 5

(

e

b

LSB down from the desired

) input and applying a small

5 000V

HEX

3V’’) This is possible only

(V

MAX

IN

This completes the ad-

IN

(

DC

256

a

b

(

)

) input Zero error

a

V

LSB (where the

) voltage which

MIN

HEX

a

)

’’ input and

LSB value

to 01

b

’’ input

IN

HEX

(

a

)