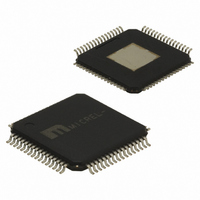

SY89538LHH Micrel Inc, SY89538LHH Datasheet - Page 4

SY89538LHH

Manufacturer Part Number

SY89538LHH

Description

IC SYNTHESIZR LVPECL/LVDS 64TQFP

Manufacturer

Micrel Inc

Series

Precision Edge®r

Type

Clock Synthesizer/Fanout Bufferr

Datasheet

1.SY89538LHH.pdf

(23 pages)

Specifications of SY89538LHH

Pll

Yes

Input

CMOS, HSTL, LVDS, LVPECL, LVTTL, SSTL, Crystal

Output

LVDS, LVPECL

Number Of Circuits

1

Ratio - Input:output

2:7

Differential - Input:output

Yes/Yes

Frequency - Max

756MHz

Divider/multiplier

Yes/No

Voltage - Supply

2.375 V ~ 3.6 V

Operating Temperature

0°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

64-TQFP Exposed Pad, 64-eTQFP, 64-HTQFP, 64-VQFP

Frequency-max

756MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Pin Description

Power

Control and Configuration

June 2006

19, 40, 43, 51

Pin Number

Pin Number

16, 30, 31,

47, 55

6, 56

2, 7

15

62

63

10

36

37

23

25

57

59

1

RSEL1, RSEL0

Exposed Pad

Pin Name

Pin Name

PSEL0

PSEL1

PSEL2

PSEL3

VCCA

VCCD

VCCO

GNDA

INSEL

GND,

LSEL

LEN

LR

LF

Pin Function

Analog PLL Power Pin. Connects to “quiet” 3.3V supply. 3.3V power pins must be

connected together on the PCB. Bypass with 0.1µF//0.01µF low ESR capacitors and

place them as close to the VCCA pin as possible.

Digital Logic Core Power Pin. VCCD connects to a 3.3V supply. All power pins must

be connected together on the PCB. Bypass with 0.1µF//0.01µF low ESR capacitors

and place them as close to the VCCD pin as possible.

LVDS and LVPECL Output Driver Power Pins. These outputs can be powered from a

2.5V or 3.3V supply. Connect all VCCO pins to the same power supply: 3.3V ±10% or

2.5V ±5%. All power pins must be connected together on the PCB. Bypass with

0.1µF//0.01µF low ESR capacitor and place them as close to the VCCO pin as

possible.

Analog PLL Ground. Connect to “quiet” ground. GNDA and GND must be connected

together on the PCB.

Ground: GND pins and exposed pad must both be connected to the same ground

plane.

Pin Function

Analog Input/Output. Provides the reference voltage for the PLL loop filter and is

used with the LF pin. See “External Loop Filter Considerations” for recommended

loop filter values.

Analog Input/Output. Provides the loop filter node for the PLL. See “External Loop

Filter Considerations” for recommended loop filter values.

TTL/CMOS Reference input pre-scalar and Zero Delay MUX divider select inputs.

The two-bit input pre-scalar divides the input reference frequency by /1, /2, /4, or /8.

RSEL0 is the LSB bit. See “Reference Input Divider and Zero Delay MUX Divider

Select Table” for proper decoding. The threshold voltage V

pull-up. The default logic is HIGH.

TTL/CMOS Input Select Control. Selects either XTAL or Reference (RFCK) input.

Internal 25kΩ pull-up. The default is logic HIGH, and selects the XTAL input. The

threshold voltage V

Logic HIGH: XTAL Select

Logic LOW: Reference Input Select

TTL/CMOS input select control signal for the LVDS LOUT0-LOUT2 outputs. LSEL,

DSEL, and LEN are used together to decode the selection and post divider of the

LVDS outputs. Internal 25kΩ pull-up. See “LVDS Output Post-Divider and Frequency

Select Table” for proper decoding. The threshold voltage V

logic is HIGH.

TTL/CMOS input enable pin. Used to control the LOUT0-LOUT2 outputs and acts as

a frequency select pin. LEN, DSEL, and LSEL are used together to decode the

selection and post divide of the LVDS output bank, see the “LVDS Output Post-

Divider and Frequency Select Table” for proper decoding. Internal 25kΩ pull-up.

When disabled, LOUT0-LOUT2 outputs are LOW, and the complimentary outputs are

HIGH. The threshold voltage V

TTL/CMOS input select control signals for the PECL POUT0-POUT3 outputs. PSELx,

DSEL and PENx are used together to decode the selection and post divider of the

PECL outputs. PSELx pins include an internal 25kΩ pull-up. The threshold voltage

V

proper decoding.

TH

= V

CC

/2. See "LVPECL Output Post-Divider and Frequency Select Table” for

TH

= V

4

CC

/2.

TH

= V

CC

/2. The default logic is HIGH.

hbwhelp@micrel.com

TH

TH

= V

= V

CC

CC

/2. The default

/2. Internal 25kΩ

or (408) 955-1690

M9999-062706-D