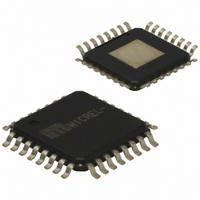

SY87729LHI Micrel Inc, SY87729LHI Datasheet - Page 6

SY87729LHI

Manufacturer Part Number

SY87729LHI

Description

IC SYNTHESIZER FRACT 3.3V 32TQFP

Manufacturer

Micrel Inc

Type

Fractional Synthesizerr

Datasheet

1.SY87729LHY.pdf

(14 pages)

Specifications of SY87729LHI

Input

PECL

Output

PECL

Frequency - Max

365MHz

Voltage - Supply

3.15 V ~ 3.45 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

32-TQFP Exposed Pad, 32-eTQFP, 32-HTQFP, 32-VQFP

Frequency-max

365MHz

For Use With

576-1404 - BOARD EVAL N SY87729 EXPERIMENT

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Micrel, Inc.

frequency 3

frequency is between 3 and 4 times the input, P is set to 4.

We need to select the P divider twice, and select the P-1

divider once. Multiplying by 4 two times out of three, and

multiplying by 3 one time out of three, averages to a

multiplication of 3

waveform is the multiplied output. The waveform in the

middle shows those edges from the output that most closely

matches a corresponding reference waveform edge.

the mux of something like “101,” so that the P divider is

selected twice, and the P-1 divider is selected once, every

three reference edges.

Fractional-N Phase-Frequency Detector

down” signals, also generates delta phase signals for use

by the lock detect circuit.

Fractional-N control block. When gated, the phase detector

generates neither pump up nor pump down pulses.

Fractional-N Charge Pump

signals from the phase-frequency detector into current

pulses. An external loop filter integrates these current pulses

into a control voltage.

gain as follows:

current is fixed at 20µA. Once the acquisition sequencer

has completed center frequency trimming, then it changes

the current of this charge pump to 50µA.

Fractional-N VCO

loop filter into a digital clock stream. The frequency of this

clock varies based on this control voltage. This VCO has a

coarse and a fine input, with a combined range of 540MHz

to 729MHz. The coarse input trims the VCO, as described

below, so that its center frequency rests near the target

frequency to generate. The fine adjustment forms part of

the closed loop. VCO gain is nominally 200MHz per Volt.

M9999-062807

hbwhelp@micrel.com or (408) 955-1690

Figure 2 shows an example generating an output

The top waveform is the reference input. The bottom

The control circuit must generate a repeating pattern to

This circuit, besides generating “pump up” and “pump

This detector circuit also accepts a gating signal from the

This circuit converts the “pump up” and “pump down”

Charge pump current is selectable. This modifies loop

During acquisition of the reference, the charge pump

This circuit converts the voltage integrated by the external

1

1

2

2

/

3

3

times the input frequency. Since the output

Figure 2. 11/3 Example

2

4

/

3

.

1

2

2

3

1

3

2

3

4

1

1

6

Fractional-N P/P-1 Divider

logical value of the output of the control block (Figure 1)

defines whether the divider divides by P (values shown in

Table 1) or by P-1. The expression for the fractional division

becomes:

which the divider must divide by P and Q

of reference clock periods during which the divider must

divide by P-1.

(Table 1) so that the voltage-controlled oscillator (VCO) of

the fractional-N PLL is not driven out of range. The following

conditions must be met:

Fractional-N Control

appropriate divide ratio, either P or P-1, in the correct pattern.

the P/P-1 divider amounts to generating a repeating binary

bit stream. In that example, a “1” represents dividing by 4,

and a “0” represents dividing by 3. The full cycle, “101,”

says to divide by 4 twice, and to divide by 3 once.

DivSel3

This is the main divider for the fractional-N loop. The

Where Q

Care should be exercised when selecting the value of P

Where,

f

f

f

This circuit controls the P/P-1 divider, selecting the

As explained in the example of Figure 2 above, controlling

Fractional division P –

f

f

VCO

VCO

REF

VCO

VCO

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

(min) = 540MHz

(max) = 729MHz

= frequency of the reference clock.

(min)

(min)

P

is the number or reference clock periods during

<

Table 1. DivSel Divider Setting

<

DivSel2

f

REF

f

REF

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

×

×

=

Fractional division

⎧

⎪

⎨

⎩ ⎪

P –

DivSel1

⎡

⎢

⎢

⎣

⎡

⎢

⎢

⎣

(

(

Q

Q

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

P–1

P–1

Q

Q

P–1

P–1

+

+

Q

Q

P

DivSel0

P

)

)

⎤

⎥

⎥

⎦

<

⎤

⎥

⎥

⎦

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

⎫

⎪

⎬

⎭ ⎪

P–1

f

VCO

<

f

VCO

is the number

(max)

AnyClock

SY87729L

(max)

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

P

or

®