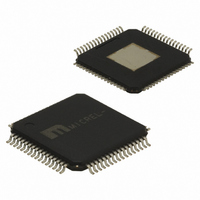

SY89538LHZ Micrel Inc, SY89538LHZ Datasheet - Page 14

SY89538LHZ

Manufacturer Part Number

SY89538LHZ

Description

3.3V LVPECL/LVDS Clock Synthesizer System (I Temp, )

Manufacturer

Micrel Inc

Series

Precision Edge®r

Type

Clock Synthesizer/Fanout Bufferr

Datasheet

1.SY89538LHY.pdf

(23 pages)

Specifications of SY89538LHZ

Pll

Yes

Input

CMOS, HSTL, LVDS, LVPECL, LVTTL, SSTL, Crystal

Output

LVDS, LVPECL

Number Of Circuits

1

Ratio - Input:output

2:7

Differential - Input:output

Yes/Yes

Frequency - Max

756MHz

Divider/multiplier

Yes/No

Voltage - Supply

2.375 V ~ 3.6 V

Operating Temperature

0°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

64-TQFP Exposed Pad, 64-eTQFP, 64-HTQFP, 64-VQFP

Frequency-max

756MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Zero Delay FBIN Input

The SY89538L features a zero delay MUX that forces

the output to be at the same phase relationship as the

reference. This effectively configures the SY89538L

as a zero delay buffer when FBSEL is logic HIGH and

the output is fed into the feedback input FBIN as

shown in Figures 3a and 3b.

January 2008

Figure 3a. Zero Delay Mode

Figure 3b. Zero Delay Mode

(LVPECL Output)

(LVDS Output)

14

How Does Zero Delay Work?

From the block diagram,

When the PLL is locked, f

Divider = FBK Divider, f

In zero delay mode, f

f

RFCK

is forced to equal f

f

REF

=

Ref.

f

RFCK

Divider

hbwhelp@micrel.com

OUT

RFCK

OUT

and

REF

is fed into FBIN, therefore,

.

f

FBK

is forced to equal f

= f

=

FBK

FBK

and since Ref.

f

Divider

FBIN

or (408) 955-1690

M9999-010808-E

FBIN

.