XC3S500E-4FTG256C Xilinx Inc, XC3S500E-4FTG256C Datasheet - Page 162

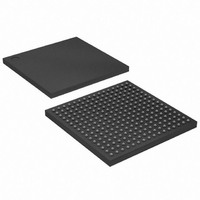

XC3S500E-4FTG256C

Manufacturer Part Number

XC3S500E-4FTG256C

Description

FPGA Spartan®-3E Family 500K Gates 10476 Cells 572MHz 90nm (CMOS) Technology 1.2V 256-Pin FTBGA

Manufacturer

Xilinx Inc

Series

Spartan™-3Er

Datasheet

1.XC3S100E-4VQG100C.pdf

(233 pages)

Specifications of XC3S500E-4FTG256C

Package

256FTBGA

Family Name

Spartan®-3E

Device Logic Cells

10476

Device Logic Units

1164

Device System Gates

500000

Number Of Registers

9312

Maximum Internal Frequency

572 MHz

Typical Operating Supply Voltage

1.2 V

Maximum Number Of User I/os

190

Ram Bits

368640

Number Of Logic Elements/cells

10476

Number Of Labs/clbs

1164

Total Ram Bits

368640

Number Of I /o

190

Number Of Gates

500000

Voltage - Supply

1.14 V ~ 1.26 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

256-LBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

122-1536 - KIT STARTER SPARTAN-3E

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

122-1485

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XC3S500E-4FTG256C

Manufacturer:

XILINX

Quantity:

1 390

Company:

Part Number:

XC3S500E-4FTG256C

Manufacturer:

XILINX

Quantity:

246

Company:

Part Number:

XC3S500E-4FTG256C

Manufacturer:

XILINX

Quantity:

1 000

Part Number:

XC3S500E-4FTG256C

Manufacturer:

XILINX/赛灵思

Quantity:

20 000

DC and Switching Characteristics

162

04/18/08

08/26/09

Date

Version

3.7

3.8

Clarified that Stepping 0 was offered only for -4C and removed Stepping 0 -5 specifications.

Added reference to XAPP459 in

to 3.465V (3.3V + 5%) in

Updated Recommended Operating Conditions for LVCMOS and PCI I/O standards in

Table

footnote recommending use of Timing Analyzer for minimum values. Updated T

T

current speed file and CLB equivalent spec. Added XC3S500E VQG100 to

Replaced T

CLKOUT_PER_JITT_FX in

Updated

Added reference to XAPP459 in

Table

SSTL in

Table 88

Table

PHFD

80. Removed Absolute Minimums from

119, and

107, and updated note 6 for

in

Table

and setup times for T

Figure 78

Table 87

MULCKID

95. Added

Table

to match current speed file. Update T

and

with T

120. Removed V

www.xilinx.com

Table 120

Table

Spread Spectrum

MSCKD

Table

DICK

77. Removed minimum input capacitance from

Table 73

Table 73

for A, B, and P registers in

107. Updated MAX_STEPS equation in

to correct CCLK active edge. Updated links.

Table 107

in

REF

Table

Revision

and

requirements for differential HSTL and differential

note 2. Updated BPI timing in

98. Added note 4 to

paragraph. Revised hold times for T

to add input jitter.

Table

Table

77. Improved recommended max V

86,

Table 92

RPW_IOB

Table

DS312-3 (v3.8) August 26, 2009

Table 106

and

in

102. Updated

Table 88

Table 93

Product Specification

Figure

Table

and note 6 to

Table

to match

and added

Table

78,

PSFD

IOICKPD

109.

96.

78.

and

CCO

in

R