ADIS16080ACCZ Analog Devices Inc, ADIS16080ACCZ Datasheet - Page 12

ADIS16080ACCZ

Manufacturer Part Number

ADIS16080ACCZ

Description

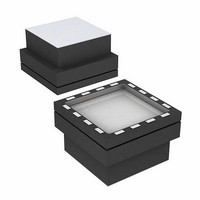

IC,Acceleration Detector,LGA,16PIN,PLASTIC

Manufacturer

Analog Devices Inc

Datasheet

1.ADIS16080PCBZ.pdf

(16 pages)

Specifications of ADIS16080ACCZ

Range °/s

±80°/s

Sensitivity

0.09766°/sec/LSB

Typical Bandwidth

40Hz

Voltage - Supply

4.75 V ~ 5.25 V

Current - Supply

7mA

Output Type

SPI

Operating Temperature

-40°C ~ 85°C

Package / Case

16-LGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

ADIS16080/PCBZ - BOARD EVALUATION FOR ADIS16080

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ADIS16080ACCZ

Manufacturer:

PHILIPS

Quantity:

570

ADIS16080

BASIC OPERATION

The ADIS16080 is designed for simple integration into indus-

trial system designs, requiring only a 5.0 V power supply and a

four-wire, industry standard serial peripheral interface (SPI). The

SPI handles all digital I/O communication in the ADIS16080.

SERIAL PERIPHERAL INTERFACE (SPI)

The ADIS16080 SPI port includes four signals: chip select ( CS ),

serial clock (SCLK), data input (DIN), and data output

(DOUT). The CS line enables the ADIS16080 SPI port and

frames each SPI event. When this signal is high, the DOUT

lines are in a high impedance state and the signals on DIN and

SCLK have no impact on operation. A complete data frame

contains 16 clock cycles. Because the SPI port operates in full

duplex mode, it supports simultaneous, 16-bit receive (DIN) and

transmit (DOUT) functions within the same data frame.

Control Register

The DIN control register provides controls for two operational

settings: the output data source and the coding (twos comple-

ment vs. offset binary). Table 5 and Figure 22 provide the

proper bit definitions for control register configuration. The

DIN sequence starts with a 1 for configuration sequences and a

0 for read sequences. When this bit is 0, the remaining DIN bits

do not change the control register and the next sample’s output

data reflects the existing configuration. Data loads from

the DIN pin into the ADIS16080 on the falling edge of SCLK.

Once the 16-SCLK sequence is complete, the control register is

updated and ready for the next read sequence. If a data frame

has less than 16 SCLK cycles, the control register does not

update and maintains its previous configuration. The DIN bit

definitions in Table 5, which have either 0 or 1 assigned to

them, are critical for proper operation.

DOUT

SCLK

DOUT

SCLK

DIN

CS

DIN

CS

WRITE

0

1

CONFIGURATION COMMAND FOR NEXT OUTPUT SEQUENCE

0

ADC PLACED IN HOLD MODE

0

DATA OUTPUT, BASED ON PREVIOUS CONFIGURATION

2

ADD1

D/C

DATA FRAME

3

ADD0

D/C

4

Figure 22. SPI Sequence, Clock Polarity = 1, Clock Phase = 0

D11

ADD1

Figure 21. Configuration and Read Sequence

5

D10

ADD0

6

D9

Rev. | Page 12 of 16

1

7

D8

1

8

D7

D/C

ADC Conversion

The chip select ( CS ) and serial clock (SCLK) lines control the

on-board A/D conversion process. When the chip select line

goes low, the DOUT line comes out of three-state mode, the

track-and-hold goes into hold mode, and the ADC samples the

analog input at this point. The track-and-hold returns to track

mode on the 14

drives the internal ADC conversion clock, using its falling edge

for control of this process. All 16 SCLK cycles are required for a

complete conversion. If a data frame has less than 16 SCLK

cycles, the conversion cannot complete and does not update the

output data for the next data frame cycle.

Output Data Access

The DOUT sequence starts with two zeros, one that clocks out

after the falling edge of CS , and a second one that clocks out on

the first SCLK falling edge. The next 14 bits, ADD0, ADD1 and

the 12 data bits, clock out on SCLK falling edges. After the 16

falling edge, the DOUT line moves to a three-state mode.

When setting up the system process to receive data from the

ADIS16080, use a clock phase setting of 0 and a clock polarity

setting of 1. These settings reflect the timing displayed in

Figure 22. To maintain proper communication at the maximum

specified clock rates, the system processor must be able to

support the setup time requirement, listed in Figure 2 and

Table 2 (t

ADC PLACED IN TRACK MODE

9

D6

D/C

10

9

).

NEXT COMMAND, IF NECESSARY

D5

0

11

th

D4

CODE

DATA FRAME

falling edge of the SCLK line. The serial clock

12

D3

D/C

13

D2

D/C

14

D1

D/C

15

D0

D/C

16

th