EA-QSB-002 Embedded Artists, EA-QSB-002 Datasheet - Page 19

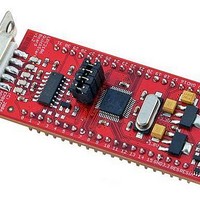

EA-QSB-002

Manufacturer Part Number

EA-QSB-002

Description

MCU, MPU & DSP Development Tools LPC2106 RS232 QUICKSTART BRD

Manufacturer

Embedded Artists

Specifications of EA-QSB-002

Processor To Be Evaluated

LPC2106

Data Bus Width

16 bit, 32 bit

Interface Type

RS-232, I2C, SPI, UART

Core

ARM7TDMI-S

Dimensions

27.9 mm x 65.3 mm

Maximum Operating Temperature

+ 85 C

Operating Supply Voltage

5 V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

NXP Semiconductors

LPC2104_2105_2106_7

Product data sheet

6.14.1 Features

6.14.2 Features available in LPC2104/2105/2106/01 only

6.15.1 Features

6.15 Watchdog timer

The LPC2104/2105/2106/01 can count external events on one of the capture inputs if the

external pulse lasts at least one half of the period of the PCLK. In this configuration,

unused capture lines can be selected as regular timer capture inputs or used as external

interrupts.

The purpose of the Watchdog is to reset the microcontroller within a reasonable amount of

time if it enters an erroneous state. When enabled, the Watchdog will generate a system

reset if the user program fails to ‘feed’ (or reload) the Watchdog within a predetermined

amount of time.

•

•

•

•

•

•

•

•

•

•

•

A 32-bit Timer/Counter with a programmable 32-bit Prescaler.

Up to four (Timer 1) and three (Timer 0) 32-bit capture channels, that can take a

snapshot of the timer value when an input signal transitions. A capture event may also

optionally generate an interrupt.

Four 32-bit match registers that allow:

– Continuous operation with optional interrupt generation on match.

– Stop timer on match with optional interrupt generation.

– Reset timer on match with optional interrupt generation.

Up to four (Timer 1) and three (Timer 0) external outputs corresponding to match

registers, with the following capabilities:

– Set LOW on match.

– Set HIGH on match.

– Toggle on match.

– Do nothing on match.

Timer can count cycles of either the peripheral clock (PCLK) or an externally supplied

clock.

When counting cycles of an externally supplied clock, only one of the timer’s capture

inputs can be selected as the timer’s clock. The rate of such a clock is limited to

PCLK

than

Internally resets chip if not periodically reloaded.

Debug mode.

Enabled by software but requires a hardware reset or a watchdog reset/interrupt to be

disabled.

Incorrect/Incomplete feed sequence causes reset/interrupt if enabled.

Flag to indicate watchdog reset.

4

1

. Duration of HIGH/LOW levels on the selected CAP input cannot be shorter

(2PCLK)

.

Rev. 07 — 20 June 2008

LPC2104/2105/2106

Single-chip 32-bit microcontrollers

© NXP B.V. 2008. All rights reserved.

19 of 41