XR17D158CV-F Exar Corporation, XR17D158CV-F Datasheet - Page 72

XR17D158CV-F

Manufacturer Part Number

XR17D158CV-F

Description

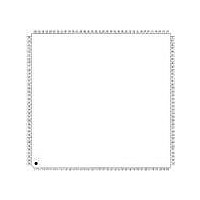

IC UART PCI BUS OCTAL 144LQFP

Manufacturer

Exar Corporation

Type

IrDA or RS- 485r

Datasheet

1.XR17D158CV-F.pdf

(73 pages)

Specifications of XR17D158CV-F

Number Of Channels

8

Package / Case

144-LQFP

Features

*

Fifo's

64 Byte

Protocol

RS485

Voltage - Supply

3.3V, 5V

With Auto Flow Control

Yes

With Irda Encoder/decoder

Yes

With False Start Bit Detection

Yes

With Modem Control

Yes

Mounting Type

Surface Mount

Data Rate

6.25 Mbps

Supply Voltage (max)

5.5 V

Supply Voltage (min)

4.5 V

Supply Current

5 mA

Maximum Operating Temperature

+ 70 C

Minimum Operating Temperature

0 C

Mounting Style

SMD/SMT

Operating Supply Voltage

5 V

No. Of Channels

8

Uart Features

Tx/Rx FIFO Counters

Supply Voltage Range

3V To 5.5V

Operating Temperature Range

0°C To +70°C

Digital Ic Case Style

LQFP

No. Of Pins

144

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Other names

1016-1291

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XR17D158CV-F

Manufacturer:

Exar Corporation

Quantity:

10 000

Part Number:

XR17D158CV-F

Manufacturer:

EXAR/艾科嘉

Quantity:

20 000

XR17D158

5V PCI BUS OCTAL UART

6.0 PROGRAMMING EXAMPLES .............................................................................................................56

ABSOLUTE MAXIMUM RATINGS...................................................................................57

ELECTRICAL CHARACTERISTICS ................................................................................57

DC ELECTRICAL CHARACTERISTICS FOR 5V PCI B

AC ELECTRICAL CHARACTERISTICS FOR 5V PCI B

DC ELECTRICAL CHARACTERISTICS FOR 3.3V PCI B

AC ELECTRICAL CHARACTERISTICS FOR 3.3V PCI B

5.3 RECEIVER ...................................................................................................................................................... 33

5.4 AUTOMATIC HARDWARE (RTS/CTS OR DTR/DSR) FLOW CONTROL OPERATION .............................. 34

5.5 INFRARED MODE .......................................................................................................................................... 36

5.6 INTERNAL LOOPBACK ................................................................................................................................. 37

5.7 UART CHANNEL CONFIGURATION REGISTERS AND ADDRESS DECODING ....................................... 38

5.8 REGISTERS .................................................................................................................................................... 40

IER versus Receive FIFO Interrupt Mode Operation................................................................................................. 41

IER versus Receive/Transmit FIFO Polled Mode Operation ..................................................................................... 41

6.1

F

F

F

T

F

F

F

T

T

T

T

T

T

T

T

T

F

F

F

F

F

F

F

F

F

IGURE

IGURE

IGURE

ABLE

IGURE

IGURE

IGURE

ABLE

ABLE

ABLE

ABLE

ABLE

ABLE

ABLE

ABLE

ABLE

IGURE

IGURE

IGURE

IGURE

IGURE

IGURE

IGURE

IGURE

IGURE

5.2.3 TRANSMITTER OPERATION IN FIFO MODE ........................................................................................................... 32

5.2.4 AUTO RS485 OPERATION ........................................................................................................................................ 32

5.3.1

5.3.2 RECEIVER OPERATION IN NON-FIFO MODE ......................................................................................................... 33

5.3.3 RECEIVER OPERATION WITH FIFO ......................................................................................................................... 34

5.8.1 RECEIVE HOLDING REGISTER (RHR) - READ-ONLY ............................................................................................ 40

5.8.2 TRANSMIT HOLDING REGISTER (THR) - WRITE-ONLY......................................................................................... 40

5.8.3 BAUD RATE GENERATOR DIVISORS (DLL AND DLM) - READ/WRITE................................................................ 40

5.8.4 INTERRUPT ENABLE REGISTER (IER) - READ/WRITE .......................................................................................... 41

5.8.5 INTERRUPT STATUS REGISTER (ISR) - READ-ONLY............................................................................................ 42

5.8.6 FIFO CONTROL REGISTER (FCR) - WRITE-ONLY .................................................................................................. 43

5.8.7 LINE CONTROL REGISTER (LCR) - READ/WRITE .................................................................................................. 46

5.8.8 MODEM CONTROL REGISTER (MCR) - READ/WRITE ........................................................................................... 47

5.8.9 LINE STATUS REGISTER (LSR) - READ/ONLY ....................................................................................................... 48

5.8.10 MODEM STATUS REGISTER (MSR) - READ-ONLY .............................................................................................. 49

5.8.11 MODEM STATUS REGISTER (MSR) - WRITE-ONLY ............................................................................................. 50

5.8.12 SCRATCH PAD REGISTER (SPR) - READ/WRITE................................................................................................. 51

5.8.13

5.8.14 ENHANCED FEATURE REGISTER (EFR) - READ/WRITE..................................................................................... 52

5.8.15 TXCNT[7:0]: TRANSMIT FIFO LEVEL COUNTER - READ-ONLY ......................................................................... 54

5.8.16 TXTRG [7:0]: TRANSMIT FIFO TRIGGER LEVEL - WRITE-ONLY ........................................................................ 54

5.8.17 RXCNT[7:0]: RECEIVE FIFO LEVEL COUNTER - READ-ONLY ............................................................................ 54

5.8.18 RXTRG[7:0]: RECEIVE FIFO TRIGGER LEVEL - WRITE-ONLY............................................................................ 54

UNLOADING RECEIVE DATA USING THE SPECIAL RECEIVE FIFO DATA WITH STATUS .................. 56

11: A

12: UART CHANNEL CONFIGURATION REGISTERS ................................................................................................... 38

13: UART CHANNEL CONFIGURATION REGISTERS DESCRIPTION. S

14: I

15: T

16: P

17: A

18: 16 S

19: S

20: UART RESET CONDITIONS ...................................................................................................................................... 55

13. T

14. R

15. R

16. A

17. I

18. I

19. T

20. PCI B

21. D

22. D

23. D

24. 5V PCI B

25. 3.3V PCI B

26. T

27. R

RECEIVE HOLDING REGISTER (RHR) .................................................................................................................... 33

NTERRUPT

FEATURE CONTROL REGISTER (FCTR) - READ/WRITE .................................................................................... 51

RANSMIT AND

UTO

ARITY SELECTION

UTO

OFTWARE

NFRARED

NTERNAL

RANSMITTER

IMING

RANSMIT

UTO

ECEIVER

ECEIVER

EVICE

EVICE

EVICE

ECEIVE

ELECTABLE

RTS/CTS

RS485 H

RTS/DTR

US

F

C

C

C

OR

D

C

US

ONFIGURATION AND

ONFIGURATION REGISTERS

ONFIGURATION

L

T

S

F

D

O

O

ATA

ONFIGURATION

OOP

US

RANSMIT

OURCE AND

LOW

ATA

PERATION IN NON

PERATION IN

E

C

R

XTERNAL

O

ALF

LOCK

C

H

R

OR

ECEIVE

PERATION IN

B

LOCK

I

YSTERESIS

C

EADY

AND

NTERRUPT AT

ACK

........................................................................................................................................................ 47

-

ONTROL

DUPLEX

DTR/DSR F

(DC

D

CTS/DSR F

................................................................................................................................................. 37

(DC

ATA

I

FIFO T

C

NTERRUPT AT

P

R

LOCK

FIFO

TO

RIORITY

S

EGISTERS

E

D

F

TO

PACE

L

NCODING AND

UNCTIONS

33MH

IRECTION

FIFO

-FIFO M

EVELS

UART R

33MH

RIGGER

I

T

AND

NPUT AT

LOW

RIGGER

R

L

LOW

Z

AND

EVEL

EGISTERS

, UART R

F

, UART R

) .......................................................................................................................... 66

W

C

Z

LOW

T

) ....................................................................................................................... 67

EGISTERS

ODE

C

ONTROL

HEN

........................................................................................................................ 53

L

RIGGER

C

F

EVEL

ONTROL

XTAL1 P

..................................................................................................................... 43

ONTROL

L

LOW

EVEL

C

.................................................................................................................. 33

R

T

ONTROL

ECEIVE

RIGGER

R

S

EGISTERS AND

C

EGISTERS AND

S

L

ELECTION

EAD AND

........................................................................................................... 68

ONTROL

R

EVEL

ELECTION

D

O

IN

EAD

ELAY FROM

II

PERATION

.................................................................................................... 61

D

M

T

.................................................................................................. 68

ATA

ABLE

ODE

O

US

US

M

W

PERATION FOR A

............................................................................................ 45

US

US

D

ODE

.......................................................................................... 34

RITE OPERATION

-D

I

......................................................................................... 34

I

ECODING

NTERFACE

NTERFACE

T

...................................................................................... 35

R

I

I

T

IS

RANSMIT

NTERFACE

NTERFACE

ECEIVE

................................................................................... 32

RANSMIT

S

ELECTED

.......................................................................... 36

D

D

HADED BITS ARE ENABLED BY

-

ATA

TO

......................................................57

......................................................58

ATA

B

................................................................. 62

YTE OR

-R

................................................................ 52

...................................................59

...................................................60

B

B

ECEIVE

URST

URST

DWORD ...................................... 63

R

W

................................................. 50

EAD

RITE

O

O

PERATION

PERATION

xr

EFR B

........................ 65

..................... 64

IT

-4. ....... 39

REV. 1.2.2