XR17C158CV-F Exar Corporation, XR17C158CV-F Datasheet - Page 29

XR17C158CV-F

Manufacturer Part Number

XR17C158CV-F

Description

IC UART PCI BUS 5V OCTAL 144LQFP

Manufacturer

Exar Corporation

Type

Universal PCI Bus Octal UARTr

Datasheet

1.XR17C158CV-F.pdf

(67 pages)

Specifications of XR17C158CV-F

Number Of Channels

8

Package / Case

144-LQFP

Features

*

Fifo's

64 Byte

Protocol

RS485

Voltage - Supply

5V

With Auto Flow Control

Yes

With Irda Encoder/decoder

Yes

With False Start Bit Detection

Yes

With Modem Control

Yes

Mounting Type

Surface Mount

Data Rate

6.25 Mbps

Supply Voltage (max)

7 V

Supply Current

5 mA

Maximum Operating Temperature

+ 85 C

Minimum Operating Temperature

- 40 C

Mounting Style

SMD/SMT

Operating Supply Voltage

7 V

No. Of Channels

8

Uart Features

High Performance, Read/Write Burst Operation

Supply Voltage Range

-0.5V To 7V

Operating Temperature Range

0°C To +70°C

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Other names

1016-1287

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XR17C158CV-F

Manufacturer:

Exar Corporation

Quantity:

10 000

Part Number:

XR17C158CV-F

Manufacturer:

EXAR/艾科嘉

Quantity:

20 000

xr

REV. 1.4.3

The host may fill the transmit FIFO with up to 64 bytes of transmit data. The THR empty flag (LSR bit-5) is set

whenever the FIFO is empty. The transmit empty interrupt (ISR bit-1) is generated when the amount of data in

the FIFO falls below its programmed trigger level (see TXTRG register) and when it empties. The transmit

empty interrupt is enabled by IER bit-1. The TSR flag (LSR bit-6) is set when TSR becomes completely empty.

Furthermore, with the RS485 half-duplex direction control enabled (FCTR bit-5=1) the source of the transmit

empty interrupt changes to TSR empty instead of THR empty. This is to ensure the RTS# output is not

changed until the last stop bit of the last character is shifted out.

The auto RS485 half-duplex direction control changes the behavior of the transmitter when enabled by FCTR

bit-5. While transmitting, the RTS# or DTR# signal is HIGH. The RTS# or DTR# signal changes from HIGH to

LOW after a specified delay indicated in MSR[7:4] following the last stop bit of the last character that has been

transmitted. This helps in turning around the transceiver to receive the remote station’s response. The delay

optimizes the time needed for the last transmission to reach the farthest station on a long cable network before

switching off the line driver. This delay prevents undesirable line signal disturbance that causes signal

degradation. It also changes the transmitter empty interrupt to TSR empty instead of THR empty.

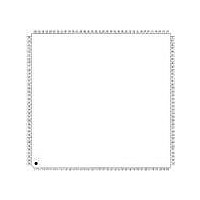

F

4.2.3

4.2.4

IGURE

10. T

(8XMODE

16X or 8X

Transmitter Operation in FIFO mode

Auto RS485 Operation

Register)

Clock

RANSMITTER

Data

Byte

O

PERATION IN NON

Transmit Shift Register (TSR)

Transmit

Register

Holding

(THR)

-FIFO M

ODE

29

THR Interrupt (ISR bit-1)

Enabled by IER bit-1

M

S

B

5V PCI BUS OCTAL UART

TXNOFIFO1

L

S

B

XR17C158