CY8C3866PVI-070 Cypress Semiconductor Corp, CY8C3866PVI-070 Datasheet - Page 68

CY8C3866PVI-070

Manufacturer Part Number

CY8C3866PVI-070

Description

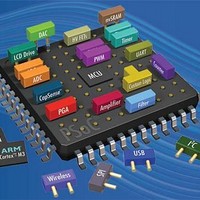

IC MCU 8BIT 64KB FLASH 48SSOP

Manufacturer

Cypress Semiconductor Corp

Series

PSOC™ 3 CY8C38xxr

Specifications of CY8C3866PVI-070

Package / Case

*

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Speed

67MHz

Number Of I /o

25

Eeprom Size

2K x 8

Core Processor

8051

Program Memory Type

FLASH

Ram Size

8K x 8

Program Memory Size

64KB (64K x 8)

Data Converters

A/D 2x20b, D/A 4x8b

Oscillator Type

Internal

Peripherals

CapSense, DMA, LCD, POR, PWM, WDT

Connectivity

CAN, EBI/EMI, I²C, LIN, SPI, UART/USART

Core Size

8-Bit

Operating Temperature (min)

-40C

Operating Temperature (max)

85C

Technology

CMOS

Processing Unit

Microcontroller

Operating Supply Voltage (min)

1.8V

Operating Supply Voltage (typ)

2.5/3.3/5V

Operating Supply Voltage (max)

5.5V

Package Type

SSOP

Screening Level

Industrial

Pin Count

48

Mounting

Surface Mount

Rad Hardened

No

Processor Series

CY8C38

Core

8051

Data Bus Width

32 bit

Data Ram Size

8 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

67 MHz

Number Of Programmable I/os

28 to 72

Number Of Timers

4

Operating Supply Voltage

0.5 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

25

Eeprom Memory Size

2KB

Ram Memory Size

8KB

Cpu Speed

67MHz

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Compliant, Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

CY8C3866PVI-070

Manufacturer:

CYPRESS厂技术支持

Quantity:

20 000

Table 11-3. AC Specifications

Document Number: 001-11729 Rev. *R

Note

F

F

Svdd

T

T

T

T

24. Based on device characterization (Not production tested).

STARTUP

SLEEP

IO_INIT

CPU

BUSCLK

HIBERNATE

Parameter

CPU frequency

Bus frequency

V

Time from V

≥ IPOR to I/O ports set to their reset

states

Time from V

≥ PRES to CPU executing code at

reset vector

Wakeup from sleep mode –

Application of non-LVD interrupt to

beginning of execution of next CPU

instruction

Wakeup from hibernate mode –

Application of external interrupt to

beginning of execution of next CPU

instruction

DD

ramp rate

Description

DDD

DDD

[24]

/V

/V

DDA

DDA

/V

/V

1.71 V

5.5 V

3.3 V

0.5 V

CCD

CCD

0 V

DC

/V

/V

CCA

CCA

Figure 11-4. F

Valid Operating Region with SMP

1.71 V ≤ V

1.71 V ≤ V

V

V

boot mode (48 MHz typ.)

V

V

IMO boot mode (12 MHz typ.)

CCA

DDA

CCA

DDA

Valid Operating Region

/V

/V

/V

/V

CPU Frequency

DDA

DDD

CCD

DDD

1 MHz

DDD

DDD

Conditions

, no PLL used, fast IMO

, no PLL used, slow

= regulated from

= regulated from

CPU

≤ 5.5 V

≤ 5.5 V

vs. V

DD

10 MHz

67 MHz

PSoC

Min

DC

DC

–

–

–

–

–

–

®

3: CY8C38 Family

Typ

–

–

–

–

–

–

–

–

Data Sheet

67.01

67.01

Max

100

10

33

66

15

Page 68 of 129

1

Units

MHz

MHz

V/ns

µs

µs

µs

µs

µs

[+] Feedback